# CS 211: Computer Architecture

Instructor: Prof. Bhagi Narahari

Dept. of Computer Science

Course URL:

www.seas.gwu.edu/~narahari/cs211/

CS211 1

## **Course Summary**

- · Technology trends

- Density increasing

- Wire delays getting longer

- » Need for simpler architectures

- Reduced instruction set is faster and simpler to implement

- · Architecture performance

- Metrics: throughput, response time, IPC, CPI

- Benchmarks

- · Review of Computer Organization

- CPU components, data paths, control path

- Sample design of a processor and its data and control path

CS211 2

# Pipeline Approach to Improve System Performance

- Analogous to fluid flow in pipelines and assembly line in factories

- Divide process into "stages" and send tasks into a pipeline

- Overlap computations of different tasks by operating on them concurrently in different stages

CS211 3

## Instruction Level Parallel Processors (ILP)

- early ILP one of two orthogonal concepts:

- pipelining vertical approach

- multiple (non-pipelined) units horizontal approach

- progression to multiple pipelined units

- instruction issue became bottleneck, led to

- superscalar ILP processors

- Very Large Instruction Word (VLIW)

- <u>Note:</u> key performance metric in all ILP processor classes is IPC (instructions per cycle)

- this is the degree of parallelism achieved

# Parallelism in Pipelining Comes From the Following Fact

While a load/store instruction is executing at the second pipeline stage, a new instruction can be initiated at the first stage.

CS211 5

3

# **Computer Pipelines**

- Execute billions of instructions, so throughput is what matters

- MIPS desirable features:

- all instructions same length,

- registers located in same place in instruction format.

- memory operands only in loads or stores

CS211 6

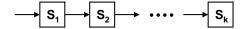

# **Linear Pipeline Processor**

Linear pipeline processes a sequence of subtasks with linear precedence At a higher level - Sequence of processors

Data flowing in streams from stage  $\boldsymbol{S}_1$  to the final stage  $\boldsymbol{S}_k$

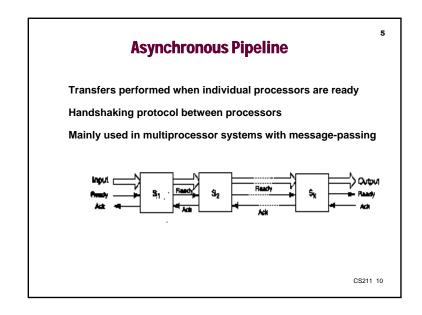

Control of data flow: synchronous or asynchronous

CS211 7

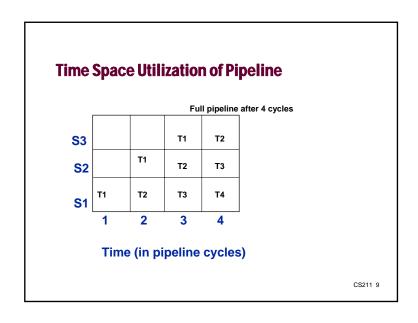

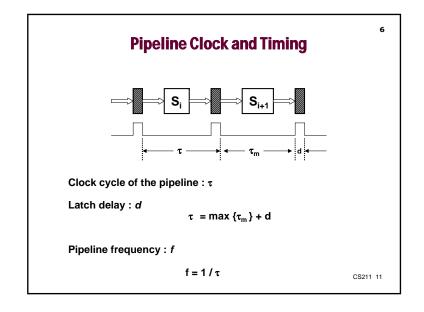

# All transfers simultaneous One task or operation enters the pipeline per cycle Processors reservation table : diagonal

#### Efficiency and Throughput

Pipeline Performance: Example

Task has 4 subtasks with time: t1=60, t2=50, t3=90, and t4=80 ns (nanoseconds)

- latch delay = 10

- Pipeline cycle time = 90+10 = 100 ns

- · For non-pipelined execution

- time = 60+50+90+80 = 280 ns

- Speedup for above case is: 280/100 = 2.8 !!

- Pipeline Time for 1000 tasks = 1000 + 4-1= 1003\*100 ns

- Sequential time = 1000\*280ns

- Throughput= 1000/1003

- What is the problem here?

- How to improve performance?

CS211 14

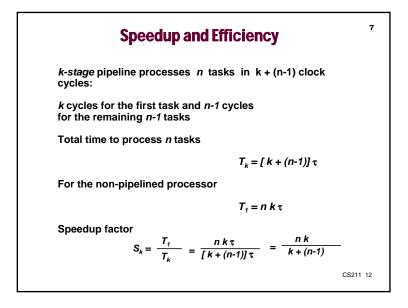

Efficiency of the k-stages pipeline:

$$E_k = \frac{S_k}{k} = \frac{n}{k + (n-1)}$$

Pipeline throughput (the number of tasks per unit time) : note equivalence to IPC

$$H_k = \frac{n}{[k + (n-1)]\tau} = \frac{n f}{k + (n-1)}$$

CS211 13

CS211 15

10

# Non-linear pipelines and pipeline control algorithms

- Can have non-linear path in pipeline...

- How to schedule instructions so they do no conflict for resources

- How does one control the pipeline at the microarchitecture level

- How to build a scheduler in hardware?

- Read notes on pipeline control!!

## **Instruction Pipeline**

- Instruction execution process lends itself naturally to pipelining

- overlap the subtasks of instruction fetch, decode and execute

#### **Announcements**

• Staughton Hall:

- Room 307 access code: 22569

Username: s307Passwd: s307

- Timing: 7am-9pm M-F

Team partners for programming assignments

- Teams of 3 persons

- Select team partner and inform instructor by Oct 1st

CS211 29

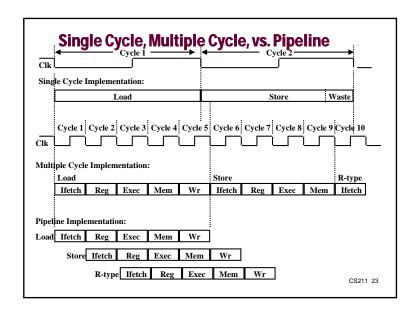

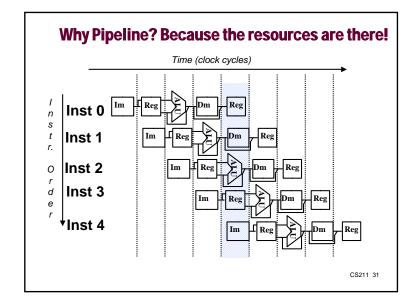

# Why Pipeline?

- Suppose we execute 100 instructions

- Single Cycle Machine

- 45 ns/cycle x 1 CPI x 100 inst = 4500 ns

- Multicycle Machine

- 10 ns/cycle x 4.6 CPI (due to inst mix) x 100 inst = 4600 ns

- Ideal pipelined machine

- 10 ns/cycle x (1 CPI x 100 inst + 4 cycle drain) = 1040 ns

CS211 30

# **Speed Up Equation for Pipelining**

$CPI_{pipelined}$  = Ideal CPI + Average Stall cycles per Inst

$Speedup = \frac{Ideal\ \textit{CPI} \times Pipeline\ depth}{Ideal\ \textit{CPI} + Pipeline\ stall\ \textit{CPI}} \times \frac{\textit{Cycle}\ Time_{unpipelined}}{\textit{Cycle}\ Time_{pipelined}}$

For simple RISC pipeline, CPI = 1:

$Speedup = \frac{Pipeline \ depth}{1 + Pipeline \ stall \ \textit{CPI}} \times \frac{\textit{Cycle Time}_{unpipelined}}{\textit{Cycle Time}_{pipelined}}$

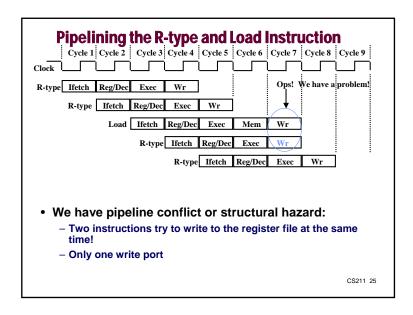

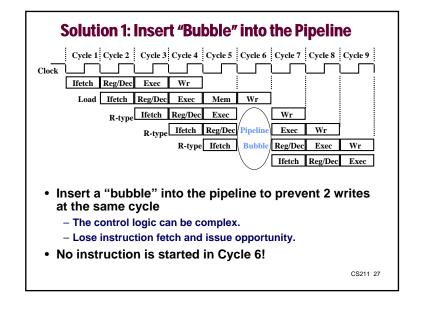

# Can pipelining get us into trouble? • Yes: Pipeline Hazards

- - structural hazards: attempt to use the same resource two different ways at the same time

- » E.g., combined washer/dryer would be a structural hazard or folder busy doing something else (watching

- data hazards: attempt to use item before it is ready

- » E.g., one sock of pair in dryer and one in washer; can't fold until get sock from washer through dryer

- » instruction depends on result of prior instruction still in the pipeline

- control hazards: attempt to make a decision before condition is evaulated

- » E.g., washing football uniforms and need to get proper detergent level; need to see after dryer before next load in

- » branch instructions

- Can always resolve hazards by waiting

- pipeline control must detect the hazard

- take action (or delay action) to resolve hazards

CS211 33

## **Its Not That Easy for Computers**

- Limits to pipelining: Hazards prevent next instruction from executing during its designated clock cycle and introduce stall cycles which increase CPI

- Structural hazards: HW cannot support this combination of instructions - two dogs fighting for the same bone

- Data hazards: Instruction depends on result of prior instruction still in the pipeline

- Control hazards: Caused by delay between the fetching of instructions and decisions about changes in control flow (branches and jumps).

CS211 34

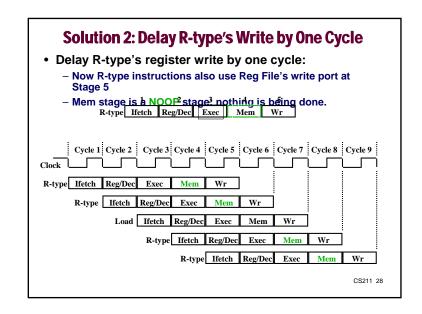

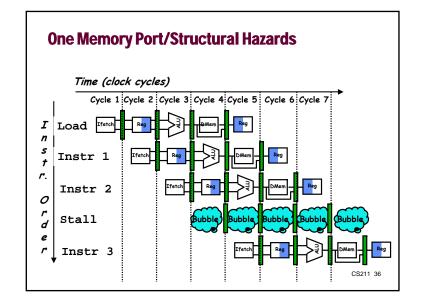

# **One Memory Port/Structural Hazards** Time (clock cycles) Cycle 1 Cycle 2 Cycle 3 Cycle 4 Cycle 5 Cycle 6 Cycle 7 Load Instr 1 Instr 2 0 Instr 3 Instr 4

## **Example: Dual-port vs. Single-port**

- Machine A: Dual ported memory ("Harvard Architecture")

- Machine B: Single ported memory, but its pipelined implementation has a 1.05 times faster clock rate

- Ideal CPI = 1 for both

- Loads are 40% of instructions executed

```

\begin{split} & \text{SpeedUp}_{\text{A}} = \text{Pipeline Depth/(1 + 0)} \times (\text{clock}_{\text{unpipe}}/\text{clock}_{\text{pipe}}) \\ & = \text{Pipeline Depth} \\ & \text{SpeedUp}_{\text{B}} = \text{Pipeline Depth/(1 + 0.4 x 1)} \times (\text{clock}_{\text{unpipe}}/(\text{clock}_{\text{unpipe}}/\ 1.05) \\ & = (\text{Pipeline Depth/1.4}) \times \ 1.05 \\ & = 0.75 \times \text{Pipeline Depth} \end{split}

```

SpeedUp<sub>A</sub> / SpeedUp<sub>B</sub> = Pipeline Depth/(0.75 x Pipeline Depth) = 1.33

Machine A is 1.33 times faster

CS211 37

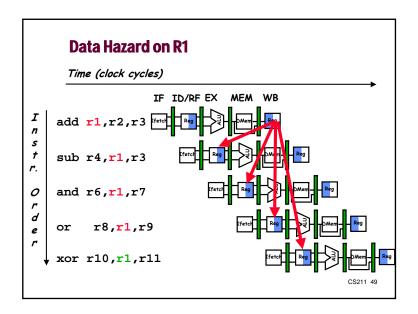

### **Data Dependencies**

- True dependencies and False dependencies

- false implies we can remove the dependency

- true implies we are stuck with it!

- Three types of data dependencies defined in terms of how succeeding instruction depends on preceding instruction

- RAW: Read after Write or Flow dependency

- WAR: Write after Read or anti-dependency

- WAW: Write after Write

CS211 38

#### **Three Generic Data Hazards**

Read After Write (RAW)

Instr<sub>J</sub> tries to read operand before Instr<sub>I</sub> writes it

```

I: add r1,r2,r3

J: sub r4,r1,r3

```

Caused by a "Dependence" (in compiler nomenclature). This hazard results from an actual need for communication.

CS211 39

## **RAW Dependency**

- Example program (a) with two instructions

- i1: load r1, a;i2: add r2, r1,r1;

- Program (b) with two instructions

- i1: mul r1, r4, r5;

- i2: add r2. r1. r1:

- Both cases we cannot read in i2 until i1 has completed writing the result

- In (a) this is due to load-use dependency

- In (b) this is due to define-use dependency

#### **Three Generic Data Hazards**

Write After Read (WAR) Instr. writes operand before Instr. reads it

```

→ I: sub r4,r1,r3

J: add r1,r2,r3

K: mul r6,r1,r7

```

- Called an "anti-dependence" by compiler writers. This results from reuse of the name "r1".

- Can't happen in MIPS 5 stage pipeline because:

- All instructions take 5 stages, and

- Reads are always in stage 2, and

- Writes are always in stage 5

CS211 41

#### **Three Generic Data Hazards**

- Write After Write (WAW) Instr, writes operand before Instr, writes it.

- Called an "output dependence" by compiler writers This also results from the reuse of name "r1".

- Can't happen in MIPS 5 stage pipeline because:

- All instructions take 5 stages, and

- Writes are always in stage 5

- Will see WAR and WAW in later more complicated pipes

```

I: sub r1,r4,r3

J: add r1,r2,r3

K: mul r6,r1,r7

```

CS211 42

# **WAR and WAW Dependency**• Example program (a):

- - i1: mul r1, r2, r3; - i2: add r2, r4, r5;

- Example program (b):

- i1: mul r1, r2, r3;

- i2: add r1, r4, r5;

- both cases we have dependence between i1 and i2

- in (a) due to r2 must be read before it is written into

- in (b) due to r1 must be written by i2 after it has been written into by i1

CS211 43

#### What to do with WAR and WAW?

- Problem:

- i1: mul r1, r2, r3; - i2: add r2, r4, r5;

- · Is this really a dependence/hazard?

#### What to do with WAR and WAW

- Solution: Rename Registers

- i1: mul r1, r2, r3;

- i2: add r6, r4, r5;

- Register renaming can solve many of these false dependencies

- note the role that the compiler plays in this

- specifically, the register allocation process--i.e., the process that assigns registers to variables

CS211 45

#### **Hazard Detection in H/W**

- Suppose instruction i is about to be issued and a predecessor instruction j is in the instruction pipeline

- How to detect and store potential hazard information

- Note that hazards in machine code are based on register usage

- Keep track of results in registers and their usage

- » Constructing a register data flow graph

- For each instruction i construct set of Read registers and Write registers

- Rregs(i) is set of registers that instruction i reads from

- Wregs(i) is set of registers that instruction i writes to

- Use these to define the 3 types of data hazards

CS211 46

#### **Hazard Detection in Hardware**

- A RAW hazard exists on register ρ if ρ ∈ Rregs(i) ∩ Wregs(j)

- Keep a record of pending writes (for inst's in the pipe) and compare with operand regs of current instruction.

- When instruction issues, reserve its result register.

- When on operation completes, remove its write reservation.

- A WAW hazard exists on register  $\rho$  if  $\rho \in \text{Wregs}(i) \cap \text{Wregs}(j)$

- A WAR hazard exists on register  $\rho$  if  $\rho \in Wregs(i) \cap Rregs(j)$

CS211 47

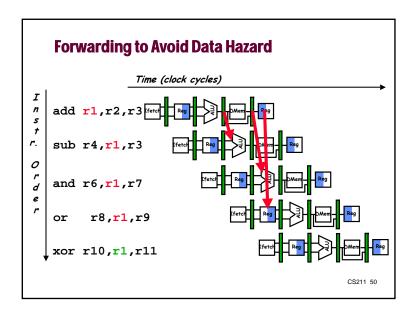

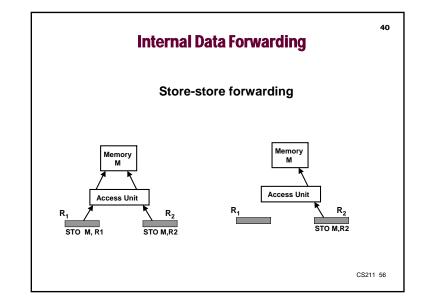

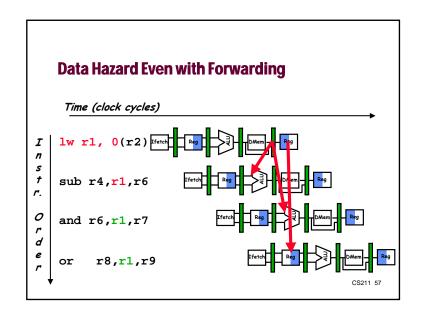

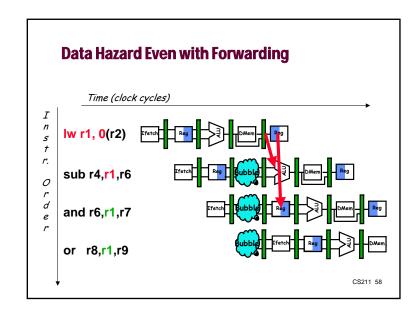

# Internal Forwarding: Getting rid of some hazards

- In some cases the data needed by the next instruction at the ALU stage has been computed by the ALU (or some stage defining it) but has not been written back to the registers

- Can we "forward" this result by bypassing stages?

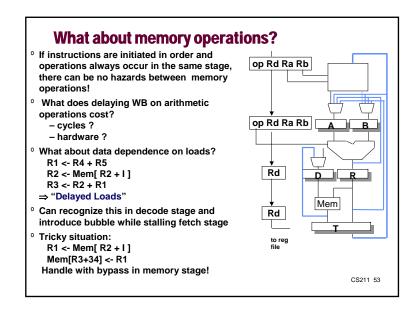

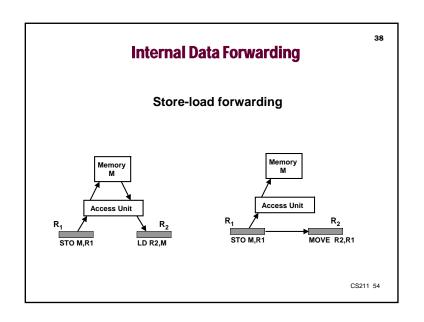

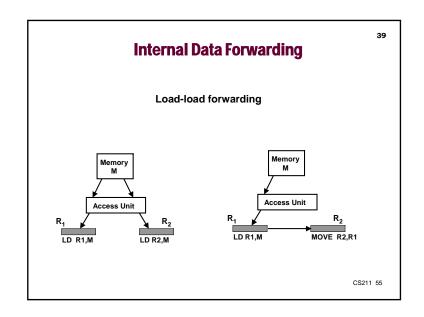

# **Internal Forwarding of Instructions**

- Forward result from ALU/Execute unit to execute unit in next stage

- Also can be used in cases of memory access

- in some cases, operand fetched from memory has been computed previously by the program

- can we "forward" this result to a later stage thus avoiding an extra read from memory?

- Who does this?

- · Internal forwarding cases

- Stage i to Stage i+k in pipeline

- store-load forwarding

- load-store forwarding

- store-store forwarding

HW Change for Forwarding

NextPC

Registers

Immediate

CS211 52

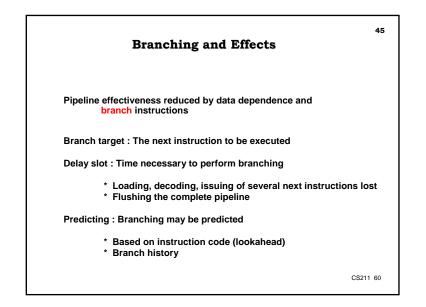

# **Branch Stall Impact**

- If CPI = 1, 30% branch, Stall 3 cycles => new CPI = 1.9!

- Two part solution:

- Determine branch taken or not sooner, AND

- Compute taken branch address earlier

- MIPS branch tests if register = 0 or ≠ 0

- MIPS Solution:

- Move Zero test to ID/RF stage

- Adder to calculate new PC in ID/RF stage

- 1 clock cycle penalty for branch versus 3

CS211 62

# Pipelined MIPS (DLX) Datapath Instruction Fetch Reg. Fetch Addr. Calc. Access This is the correct 1 cycle latency implementation! CS211 63

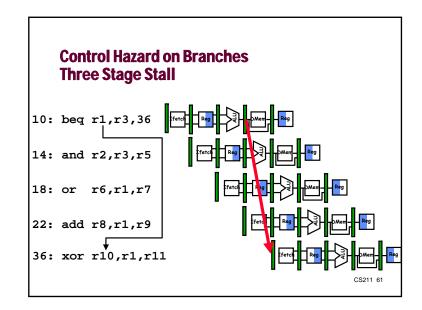

#### **Four Branch Hazard Alternatives**

#1: Stall until branch direction is clear - flushing pipe

#### #2: Predict Branch Not Taken

- Execute successor instructions in sequence

- "Squash" instructions in pipeline if branch actually taken

- Advantage of late pipeline state update

- 47% DLX branches not taken on average

- PC+4 already calculated, so use it to get next instruction

#### #3: Predict Branch Taken

- 53% DLX branches taken on average

- But haven't calculated branch target address in DLX

- » DLX still incurs 1 cycle branch penalty

- » Other machines: branch target known before outcome

# **Four Branch Hazard Alternatives**

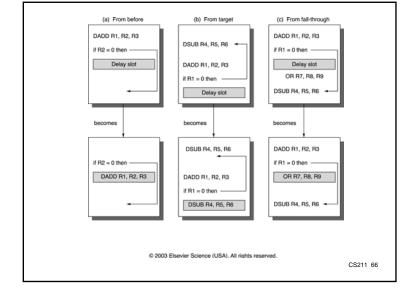

#### #4: Delayed Branch

- Define branch to take place AFTER a following instruction

```

branch instruction

sequential successor,

sequential successor,

sequential successor,

sequential successor,

branch target if taken

Branch delay of length n

```

- 1 slot delay allows proper decision and branch target address in 5 stage pipeline

- DLX uses this

CS211 65

# **Delayed Branch**

- · Where to get instructions to fill branch delay slot?

- Before branch instruction

- From the target address: only valuable when branch taken

- From fall through: only valuable when branch not taken

- Cancelling branches allow more slots to be filled

- Compiler effectiveness for single branch delay slot:

- Fills about 60% of branch delay slots

- About 80% of instructions executed in branch delay slots useful in computation

- About 50% (60% x 80%) of slots usefully filled

- Delayed Branch downside: 7-8 stage pipelines, multiple instructions issued per clock (superscalar)

CS211 67

# **Evaluating Branch Alternatives**

Pipeline speedup =  $\frac{\text{Pipeline depth}}{1 + \text{Branch frequency} \times \text{Branch penalty}}$

|                   | ranch<br>enalty | CPI  | speedup v.<br>unpipelined | speedup v.<br>stall |

|-------------------|-----------------|------|---------------------------|---------------------|

| Stall pipeline    | 3               | 1.42 | 3.5                       | 1.0                 |

| Predict taken     | 1               | 1.14 | 4.4                       | 1.26                |

| Predict not taken | 1               | 1.09 | 4.5                       | 1.29                |

| Delayed branch    | 0.5             | 1.07 | 4.6                       | 1.31                |

Conditional & Unconditional = 14%, 65% change PC

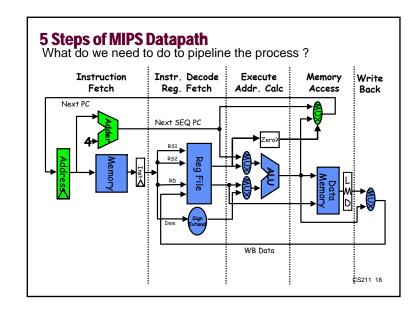

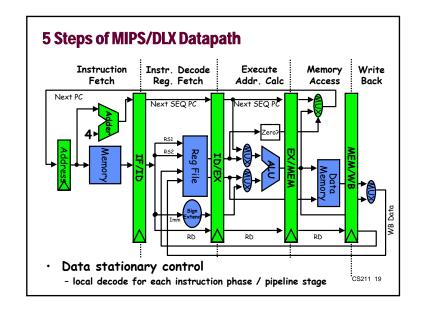

# **Designing a Pipelined Processor**

- Go back and examine your datapath and control diagram

- · associated resources with states

- ensure that flows do not conflict, or figure out how to resolve

- assert control in appropriate stage

CS211 69

# **Summary: Control and Pipelining**

- · Just overlap tasks; easy if tasks are independent

- Speed Up ≤ Pipeline Depth; if ideal CPI is 1, then:

$$Speedup = \frac{Pipeline \ depth}{1 + Pipeline \ stall \ \textit{CPI}} \times \frac{\textit{Cycle Time}_{unpipelined}}{\textit{Cycle Time}_{pipelined}}$$

- Hazards limit performance on computers:

- Structural: need more HW resources

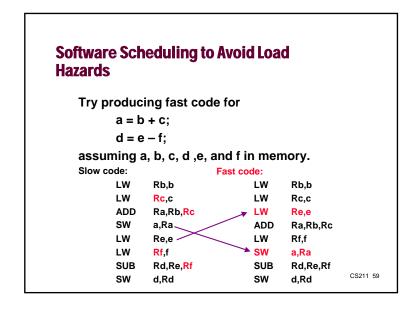

- Data (RAW,WAR,WAW): need forwarding, compiler scheduling

- Control: delayed branch, prediction

CS211 71

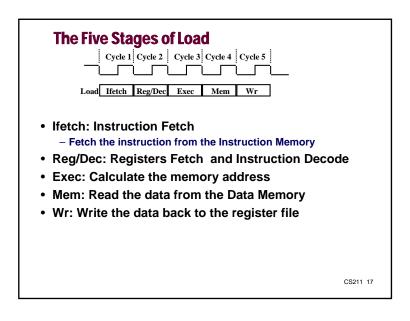

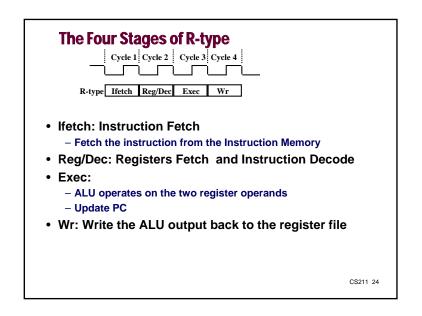

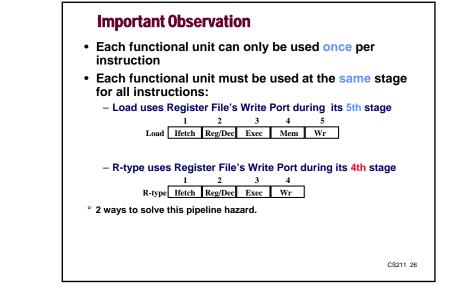

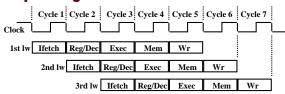

# **Pipelining the Load Instruction**

- The five independent functional units in the pipeline datapath are:

- Instruction Memory for the lfetch stage

- Register File's Read ports (bus A and busB) for the Reg/Dec stage

- ALU for the Exec stage

- Data Memory for the Mem stage

- Register File's Write port (bus W) for the Wr stage

CS211 70

## **Summary #1/2: Pipelining**

- · What makes it easy

- all instructions are the same length

- just a few instruction formats

- memory operands appear only in loads and stores

- What makes it hard? HAZARDS!

- structural hazards: suppose we had only one memory

- control hazards: need to worry about branch instructions

- data hazards: an instruction depends on a previous instruction

- Pipelines pass control information down the pipe just as data moves down pipe

- · Forwarding/Stalls handled by local control

- Exceptions stop the pipeline

## **Summary #2/2**

- Pipelines pass control information down the pipe just as data moves down pipe

- · Forwarding/Stalls handled by local control

- Exceptions stop the pipeline

- MIPS I instruction set architecture made pipeline visible (delayed branch, delayed load)

- More performance from deeper pipelines, parallelism

CS211 73

#### **Introduction to ILP**

- What is ILP?

- Processor and Compiler design techniques that speed up execution by causing individual machine operations to execute in parallel

- ILP is transparent to the user

- Multiple operations executed in parallel even though the system is handed a single program written with a sequential processor in mind

- Same execution hardware as a normal RISC machine

- May be more than one of any given type of hardware

CS211 75

#### **ILP Processors**

whereas pipelined processors work like an assembly line, both VLIW and Superscalar processors operate basically in parallel, making use of a number of concurrently working execution units (EU)