## Next Generation Hardware Monitoring Infrastructure for Multi-core Resource Auditing

by

Jie Chen

A Dissertation submitted to

The Faculty of

The School of Engineering and Applied Science of the George Washington University in partial satisfaction of the requirements for the degree of Doctor of Philosophy

Oct, 2014

Dissertation Advisor: Dr. Guru Prasadh Venkataramani Assistant Professor of Engineering and Applied Science

#### Abstract

Thesis Statement: Performance counters in hardware have been very successful in providing feedback about application performance to programmers and compilers. With the growing relevance of understanding power, energy and security (information leakage), we envision that the next generation hardware monitoring infrastructure will support these features. In this work, we study the design and implementation of such hardware monitors.

Continuous advances in semiconductor technologies have enabled the integration of billions of transistors in modern multicore processors. This offers software applications with abundant hardware resources to use. To realize more parallelism and higher performance, software developers are concerned about characterizing and optimizing their applications over the usage of hardware resources. At the same time, hardware monitoring infrastructure in most current processors offers a collection of hardware counters for auditing architectural events on hardware units. Such counters can be used by programmers and performance analysts for auditing performance bottlenecks and consequently, optimizing application performance. In recent years, there is a surging demand for improving application power, energy and information leakage beyond performance, due to increasing complexity in power delivery within the chip and vast amount of shared hardware resources between applications running on the processors.

As power budget is limited, it becomes necessary to audit software power usages and look for power optimizations *at all levels* to better utilize the limited power. Optimizing the applications for energy is necessary due to the impact that they have on system operation and costs. Inefficient software has been often cited as a major reason for wasteful energy consumption in computing systems. It is essential for programmers to audit the energy usage of their program code and apply code optimizations for better energy. While power and energy are already among the top issues that need to be solved, a fast growing concern is information leakage using shared resource in multi-core hardware. Over the past years, it has been shown many times that multicore hardware resources are vulnerable and can easily be exploited as covert timing channels to leak sensitive information at very high bandwidth. Unfortunately, there is no existing hardware-supported auditing for such information leakage.

As these set of factors such as power, energy and information leakage are becoming more critical, software developers and system administrators are urgently looking for appropriate tools to address such challenges, just like they used to rely on performance counters for performance tuning. The next generation hardware monitoring infrastructure should take users' need into consideration, and provide sufficient and convenient resource auditing support *be*-*yond just performance*. It will not only enable the programmers to improve the scalability of their softwares by better utilizing power budget and to reduce cost by improving the energy efficiency of their program code, but also help system administrators enhance the level of trust of their systems by tracking and removing information leakage sources.

In this dissertation, we proposed and explored the design of three novel resource auditing techniques as part of the next generation hardware monitoring infrastructure, namely, application power auditing, application energy auditing, and covert timing channel auditing. The design methodologies of these three techniques share the same goal of leveraging hardware support to enable the gathering of advance resource usage information in an efficient and cost-effective manner. These hardware support are also equipped with lightweight software support to maximize flexibility in usage. Overall, our contributions push the hardware monitoring support to the next new level, and enable the programmer to efficiently address a spectrum of existing and emerging system issues.

# Contents

|          | Abs  | stract                                                                    | i          |

|----------|------|---------------------------------------------------------------------------|------------|

|          | Cor  | ntents                                                                    | iii        |

|          | List | of Figures                                                                | v          |

|          | List | of Tables                                                                 | <b>iii</b> |

| 1        | Intr | roduction                                                                 | <b>2</b>   |

|          | 1.1  | Need for Next Generation Hardware Monitoring                              | 2          |

|          | 1.2  | Multicore Resource Usage Problems– Power, Energy, and Information Leakage | 3          |

|          | 1.3  | Overview                                                                  | 6          |

|          | 1.4  | Scope of this Dissertation                                                | 7          |

| <b>2</b> | Bac  | kground                                                                   | 8          |

|          | 2.1  | Application Power Auditing                                                | 8          |

|          | 2.2  | Application Energy Auditing                                               | 9          |

|          | 2.3  | Information Leakage Auditing                                              | 10         |

| 3        | Wat  | tts-inside: Application Power Auditing                                    | 13         |

|          | 3.1  | Motivation – Understanding Multicore Power                                | 13         |

|          | 3.2  | Design Overview                                                           | 15         |

|   |                          | 3.2.1                                                                                    | Hardware Support                                                                                                                                                                                                                                                                                                                                                                                   | 15                                                                                                                                 |

|---|--------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|   |                          | 3.2.2                                                                                    | Software Support                                                                                                                                                                                                                                                                                                                                                                                   | 19                                                                                                                                 |

|   | 3.3                      | Imple                                                                                    | nentation                                                                                                                                                                                                                                                                                                                                                                                          | 22                                                                                                                                 |

|   |                          | 3.3.1                                                                                    | Hardware Support                                                                                                                                                                                                                                                                                                                                                                                   | 22                                                                                                                                 |

|   |                          | 3.3.2                                                                                    | Software Support                                                                                                                                                                                                                                                                                                                                                                                   | 24                                                                                                                                 |

|   | 3.4                      | Exper                                                                                    | imental Setup                                                                                                                                                                                                                                                                                                                                                                                      | 24                                                                                                                                 |

|   | 3.5                      | Evalua                                                                                   | ation                                                                                                                                                                                                                                                                                                                                                                                              | 26                                                                                                                                 |

|   |                          | 3.5.1                                                                                    | Adaptive Filter vs. Ideal Filter                                                                                                                                                                                                                                                                                                                                                                   | 26                                                                                                                                 |

|   |                          | 3.5.2                                                                                    | Sampling                                                                                                                                                                                                                                                                                                                                                                                           | 27                                                                                                                                 |

|   |                          | 3.5.3                                                                                    | Scalability of CSPPV Memory Log                                                                                                                                                                                                                                                                                                                                                                    | 28                                                                                                                                 |

|   |                          | 3.5.4                                                                                    | Area, Power and Latency of Watts-inside Hardware                                                                                                                                                                                                                                                                                                                                                   | 28                                                                                                                                 |

|   |                          | 3.5.5                                                                                    | Case study – Improving Load/Store Queue power consumption                                                                                                                                                                                                                                                                                                                                          | 29                                                                                                                                 |

|   | 3.6                      | Relate                                                                                   | d Work                                                                                                                                                                                                                                                                                                                                                                                             | 33                                                                                                                                 |

|   | 0 7                      | Current                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                    | 34                                                                                                                                 |

|   | 3.7                      | Summ                                                                                     | ary                                                                                                                                                                                                                                                                                                                                                                                                | 54                                                                                                                                 |

| 4 |                          |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                    |

| 4 | enD                      | )ebug:                                                                                   | Application Energy Auditing                                                                                                                                                                                                                                                                                                                                                                        | 35                                                                                                                                 |

| 4 | <b>enD</b><br>4.1        | <b>)ebug:</b><br>Under                                                                   | Application Energy Auditing         standing Application Energy                                                                                                                                                                                                                                                                                                                                    | <b>35</b><br>35                                                                                                                    |

| 4 | enD                      | <b>)ebug:</b><br>Under                                                                   | Application Energy Auditing                                                                                                                                                                                                                                                                                                                                                                        | 35                                                                                                                                 |

| 4 | <b>enD</b><br>4.1        | <b>)ebug:</b><br>Under                                                                   | Application Energy Auditing         standing Application Energy                                                                                                                                                                                                                                                                                                                                    | <b>35</b><br>35                                                                                                                    |

| 4 | <b>enD</b><br>4.1        | <b>)ebug:</b><br>Under<br>Fine-g                                                         | Application Energy Auditing         standing Application Energy         rain Energy Profiling                                                                                                                                                                                                                                                                                                      | <b>35</b><br>35<br>37                                                                                                              |

| 4 | <b>enD</b><br>4.1        | Debug:<br>Under<br>Fine-g<br>4.2.1<br>4.2.2                                              | Application Energy Auditing         standing Application Energy         rain Energy Profiling         Energy Model Using Performance Counters                                                                                                                                                                                                                                                      | <b>35</b><br>35<br>37<br>38                                                                                                        |

| 4 | <b>enD</b><br>4.1<br>4.2 | Debug:<br>Under<br>Fine-g<br>4.2.1<br>4.2.2                                              | Application Energy Auditing         standing Application Energy         rain Energy Profiling         Energy Model Using Performance Counters         Attributing Energy to Program Functions                                                                                                                                                                                                      | <b>35</b><br>35<br>37<br>38<br>39                                                                                                  |

| 4 | <b>enD</b><br>4.1<br>4.2 | Debug:<br>Under<br>Fine-g<br>4.2.1<br>4.2.2<br>Auton                                     | Application Energy Auditing         standing Application Energy         rain Energy Profiling         Energy Model Using Performance Counters         Attributing Energy to Program Functions         nated Recommendation System for Energy Optimization                                                                                                                                          | <ul> <li>35</li> <li>35</li> <li>37</li> <li>38</li> <li>39</li> <li>41</li> </ul>                                                 |

| 4 | <b>enD</b><br>4.1<br>4.2 | Debug:<br>Under<br>Fine-g<br>4.2.1<br>4.2.2<br>Auton<br>4.3.1                            | Application Energy Auditing         standing Application Energy         rain Energy Profiling         call and the energy Model Using Performance Counters         Attributing Energy to Program Functions         nated Recommendation System for Energy Optimization         Basics of Genetic Programming                                                                                       | <ul> <li>35</li> <li>35</li> <li>37</li> <li>38</li> <li>39</li> <li>41</li> <li>42</li> </ul>                                     |

| 4 | <b>enD</b><br>4.1<br>4.2 | Debug:<br>Under<br>Fine-g<br>4.2.1<br>4.2.2<br>Auton<br>4.3.1<br>4.3.2                   | Application Energy Auditing         standing Application Energy         rain Energy Profiling         rain Energy Model Using Performance Counters         Attributing Energy to Program Functions         nated Recommendation System for Energy Optimization         Basics of Genetic Programming         Artificial Selection Genetic Programming                                              | <ul> <li>35</li> <li>35</li> <li>37</li> <li>38</li> <li>39</li> <li>41</li> <li>42</li> <li>43</li> </ul>                         |

| 4 | <b>enD</b><br>4.1<br>4.2 | Debug:<br>Under<br>Fine-g<br>4.2.1<br>4.2.2<br>Auton<br>4.3.1<br>4.3.2<br>4.3.3          | Application Energy Auditing         standing Application Energy         rain Energy Profiling         rain Energy Model Using Performance Counters         Attributing Energy to Program Functions         nated Recommendation System for Energy Optimization         Basics of Genetic Programming         Attrificial Selection Genetic Programming         ASGP Algorithm                      | <ul> <li>35</li> <li>35</li> <li>37</li> <li>38</li> <li>39</li> <li>41</li> <li>42</li> <li>43</li> <li>43</li> </ul>             |

| 4 | <b>enD</b><br>4.1<br>4.2 | Debug:<br>Under<br>Fine-g<br>4.2.1<br>4.2.2<br>Auton<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4 | Application Energy Auditing         standing Application Energy         rain Energy Profiling         Energy Model Using Performance Counters         Attributing Energy to Program Functions         nated Recommendation System for Energy Optimization         Basics of Genetic Programming         Artificial Selection Genetic Programming         ASGP Algorithm         Neutral Transforms | <ul> <li>35</li> <li>35</li> <li>37</li> <li>38</li> <li>39</li> <li>41</li> <li>42</li> <li>43</li> <li>43</li> <li>47</li> </ul> |

### CONTENTS

| 6        | Con | clusio | ns and Future Work                               | 90 |

|----------|-----|--------|--------------------------------------------------|----|

|          | 5.7 | Summ   | ary                                              | 88 |

|          | 5.6 | Relate | d Work                                           | 86 |

|          |     | 5.5.4  | Testing for False Alarms                         | 84 |

|          |     | 5.5.3  | Varying Cache Channel Implementations            | 84 |

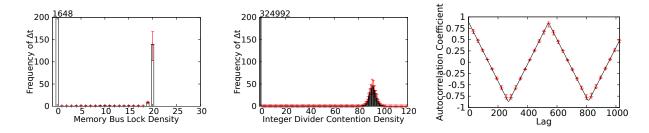

|          |     | 5.5.2  | Encoded Message patterns                         | 84 |

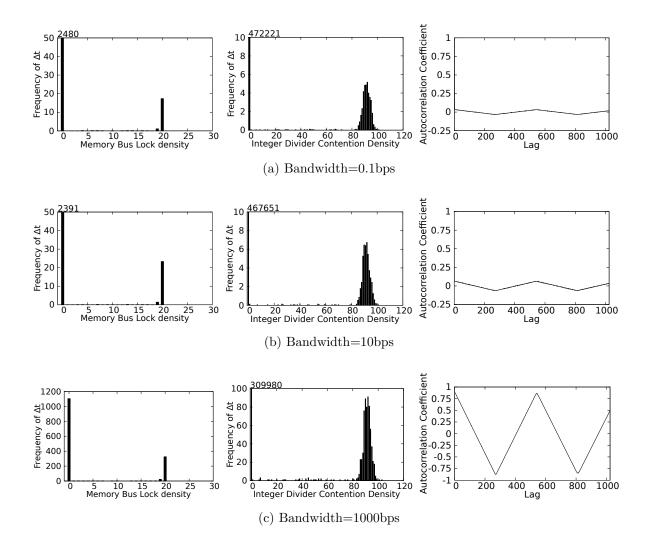

|          |     | 5.5.1  | Varying Bandwidth Rates                          | 81 |

|          | 5.5 | Evalua | ation and Sensitivity Study                      | 81 |

|          |     | 5.4.2  | Software Support                                 | 80 |

|          |     | 5.4.1  | Hardware Support                                 | 77 |

|          | 5.4 | Impler | nentation                                        | 77 |

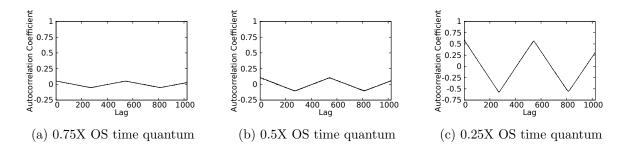

|          |     | 5.3.4  | Oscillatory Pattern Detection                    | 74 |

|          |     | 5.3.3  | Covert Timing Channel on Memory                  | 73 |

|          |     | 5.3.2  | Recurrent Burst Pattern Detection                | 69 |

|          |     | 5.3.1  | Covert Timing Channels on Combinational hardware | 67 |

|          | 5.3 | Design | Overview                                         | 66 |

|          | 5.2 | Threat | t Model and Assumptions                          | 65 |

|          | 5.1 | Under  | standing Covert Timing Channels                  | 64 |

| <b>5</b> | CC- | Hunte  | er: Information Leakage Auditing                 | 64 |

|          | 4.6 | Summ   | ary                                              | 62 |

|          |     | 4.5.2  | Energy Optimization                              | 61 |

|          |     | 4.5.1  | Energy Estimation                                | 60 |

|          | 4.5 | Relate | d Work                                           | 60 |

|          |     | 4.4.1  | Validation on a real system                      | 58 |

|          |     |        |                                                  |    |

# List of Figures

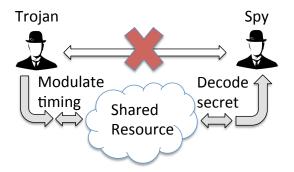

| 2.1 | A Covert Timing Channel using timing modulation on a shared resource to                  |    |

|-----|------------------------------------------------------------------------------------------|----|

|     | divulge secrets                                                                          | 11 |

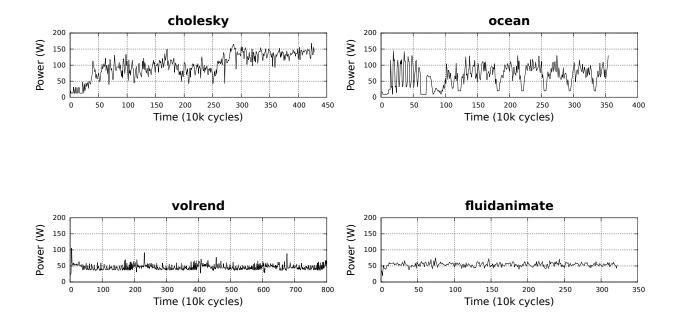

| 3.1 | Dynamic Power traces for four-threaded applications measured during their                |    |

|     | execution                                                                                | 14 |

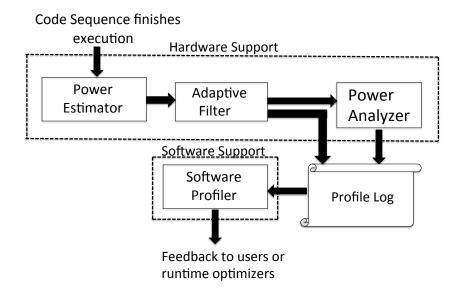

| 3.2 | Design overview of the Watts-inside framework                                            | 16 |

| 3.3 | Code Sequence Power Profile Vector (CSPPV)                                               | 18 |

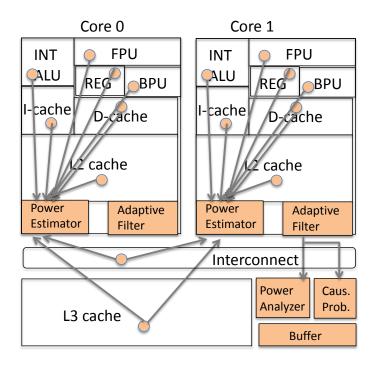

| 3.4 | Hardware modifications needed for Watts-inside framework                                 | 23 |

| 3.5 | Ideal Filter rate for capture ratios of $0.25$ , $0.1$ and $0.05$ . The right axis shows |    |

|     | the number of code sequences that are executed across all four threads                   | 25 |

| 3.6 | Adaptive Filter rate for capture ratios of $0.25$ , $0.1$ and $0.05$ . The right axis    |    |

|     | shows the number of code sequences that are executed across all four threads.            | 25 |

| 3.7 | Average relative error in the mean and standard deviation of power consump-              |    |

|     | tion by code sequences (in Splash-2 and Parsec-1.0 applications) due to sam-             |    |

|     | pling, relative to a baseline execution without sampling                                 | 27 |

| 3.8 | Average and worst-case CSPPV Memory log requirements for capture ra-                     |    |

|     | tio=0.25 for different numbers of cores                                                  | 28 |

| 3.9 | Code snippets from ocean and streamcluster benchmarks where store-to-load                |    |

|     | dependencies result in high power                                                        | 30 |

|     |                                                                                          |    |

### LIST OF FIGURES

| 3.10 | Modified code snippets from ocean and streamcluster benchmarks that no          |    |

|------|---------------------------------------------------------------------------------|----|

|      | longer have store-to-load dependencies                                          | 31 |

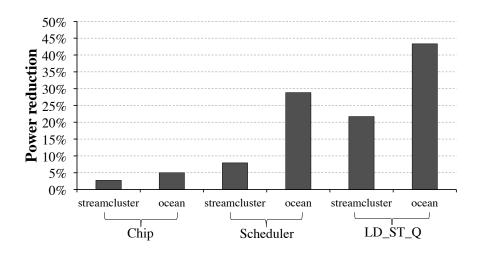

| 3.11 | Power reduction across the entire chip, scheduler and load/store queue after    |    |

|      | removing store-to-load dependencies                                             | 32 |

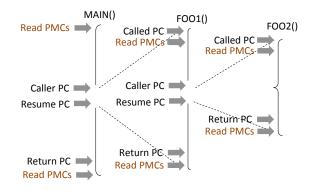

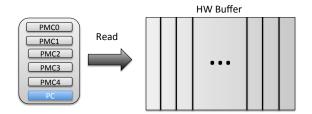

| 4.1  | Recording performance counters and PCs at function calls and returns            | 40 |

| 4.2  | Storing performance counters and PCs to the hardware buffer                     | 40 |

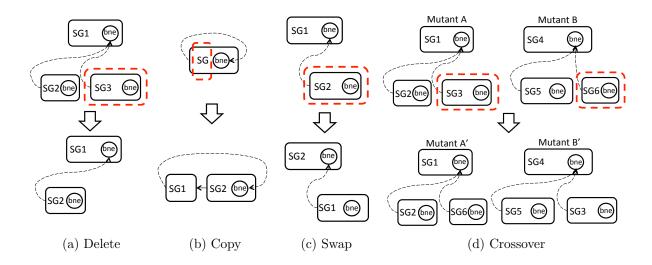

| 4.3  | Examples of Genetic operator Applications on CDDG                               | 49 |

| 4.4  | Fmm code snippet                                                                | 55 |

| 4.5  | Ocean code snippet                                                              | 56 |

| 4.6  | Cholesky code snippet                                                           | 57 |

| 4.7  | Water-sp/Water-n2 code snippet                                                  | 57 |

| 4.8  | Fluidanimate code snippet                                                       | 58 |

| 4.9  | Streamcluster code snippet                                                      | 58 |

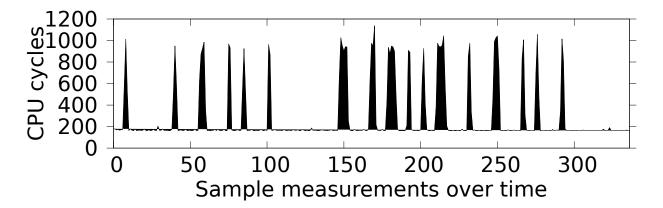

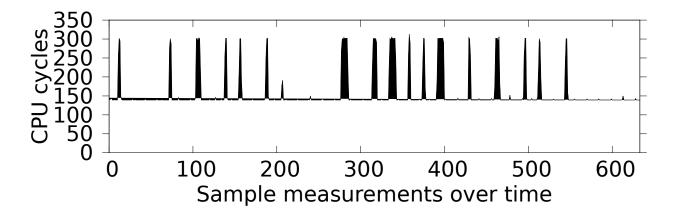

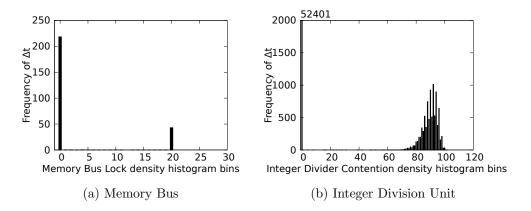

| 5.1  | Average latency per memory access (in CPU cycles) in Memory Bus Covert          |    |

|      | Channel                                                                         | 68 |

| 5.2  | Average loop execution time (in CPU cycles) in Integer Divider Covert Channel   | 69 |

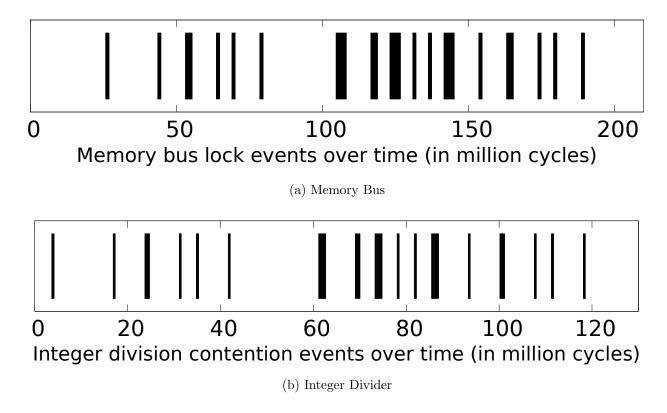

| 5.3  | Event Train plots for Memory Bus and Integer Divider showing burst patterns.    | 70 |

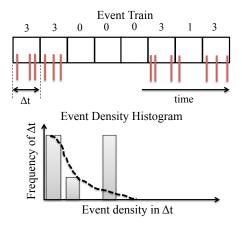

| 5.4  | Illustration of Event Train and its corresponding Event Density Histogram.      |    |

|      | The distibution is compared against the Poisson Distribution shown by the       |    |

|      | dotted line to detect presence of burst patterns                                | 71 |

| 5.5  | Event Density Histograms for Covert Timing Channels using Memory Bus            |    |

|      | and Integer Divider.                                                            | 71 |

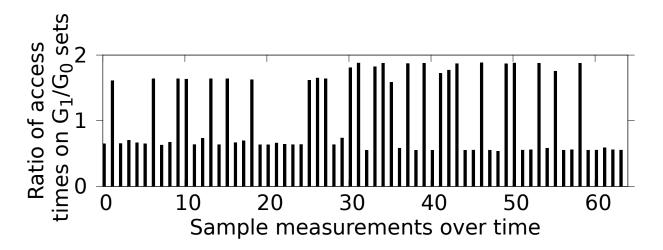

| 5.6  | Ratios of cache access times between $G_1$ and $G_0$ cache sets in Cache Covert |    |

|      | Channel                                                                         | 74 |

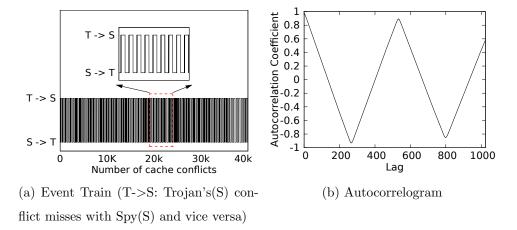

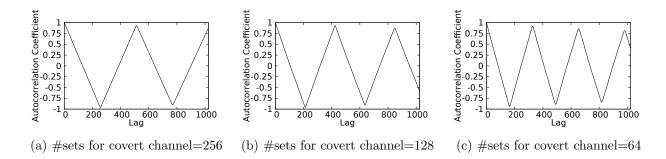

| 5.7  | Oscillatory pattern of cache conflict misses between trojan and spy. An auto-   |    |

|      | obeliatory pattern of cache connect misses between trojan and spy. Thi auto     |    |

| 5.8  | Hardware Implementation and integration of CC-Hunter into processor hard-    |    |

|------|------------------------------------------------------------------------------|----|

|      | ware                                                                         | 77 |

| 5.9  | Bandwidth test using Memory Bus, Integer Divider and Cache Covert Channels   | 82 |

| 5.10 | Autocorrelograms for 0.1 bps cache covert channels at reduced observation    |    |

|      | window sizes                                                                 | 83 |

| 5.11 | Test with 256 randomly generated 64-bit messages on Memory Bus, Integer      |    |

|      | Divider and Cache covert channels. Black (thick) bars are the means, and the |    |

|      | red (annotations) arrows above them show the range (min, max). $\ldots$ .    | 83 |

| 5.12 | Autocorrelograms for cache covert channel with varying numbers of cache sets |    |

|      | for communication.                                                           | 83 |

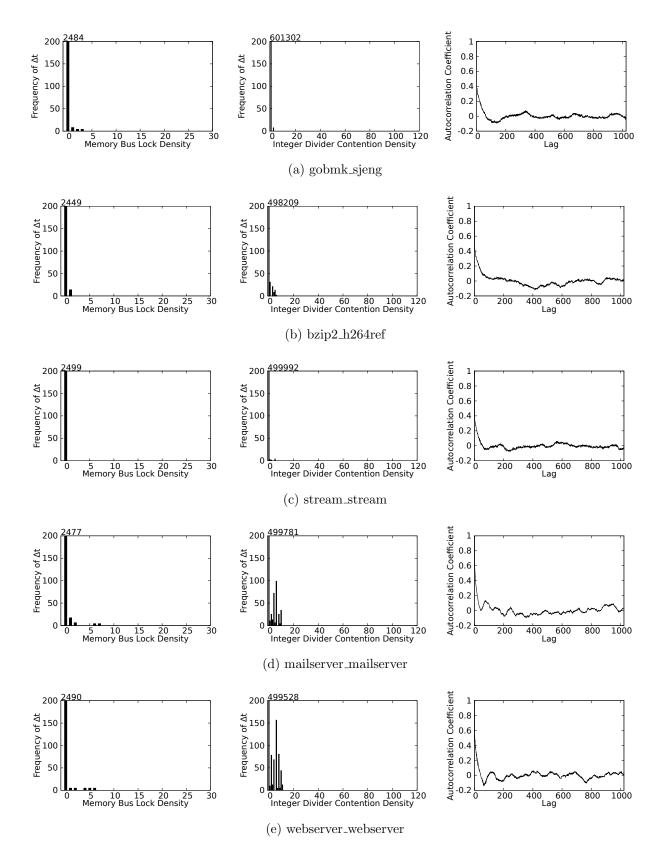

| 5.13 | Event Density Histograms and Autocorrelograms in pair combinations of        |    |

|      | SPEC2k6, Stream & Filebench                                                  | 87 |

# List of Tables

| 3.1 | Performance and Dynamic Power imbalance in SPLASH-2 and PARSEC-1.0                     |    |

|-----|----------------------------------------------------------------------------------------|----|

|     | benchmarks with four threads                                                           | 15 |

| 3.2 | Area, Power and Latency Estimates of Watts-inside hardware                             | 29 |

| 4.1 | Energy and performance profile of functions in Splash-2 and PARSEC-1.0                 |    |

|     | benchmarks with 8 threads                                                              | 35 |

| 4.2 | Processor Configuration and Power Model                                                | 36 |

| 4.3 | Triggering heuristics for genetic operators                                            | 50 |

| 4.4 | Number of mutants for the un-guided natural selection GP algorithm $\ldots$ .          | 51 |

| 4.5 | Number of mutant for our ASGP algorithm with triggering heuristics $\ldots$ .          | 51 |

| 4.6 | Execution time overhead comparison between the natural selection GP algo-              |    |

|     | rithm and our heuristic-triggered ASGP algorithm                                       | 52 |

| 4.7 | Energy reduction for our benchmark applications in simulator (Baseline: GCC            |    |

|     | -O3)                                                                                   | 59 |

| 4.8 | Energy reduction on a real system (Intel Core i7) $\ldots \ldots \ldots \ldots \ldots$ | 60 |

| 5.1 | Area, Power and Latency Estimates of CC-Auditor                                        | 80 |

## Chapter 1

## Introduction

## 1.1 Need for Next Generation Hardware Monitoring

As software is getting more complex, efficiently characterizing and optimizing applications has posed great challenges for programmers and system administrators. Hardware monitoring has become a very popular option for them to address such challenges. Hardware monitoring infrastructure provides collections of highly efficient on-chip performance counters that can gather critical architectural statistics at application runtime. These profile-based data can be used for analyzing program behaviors, identifying performance bottlenecks, and ultimately, improving the overall system performance. The importance and usefulness of hardware monitors have already been justified by the popularity of software tools that access hardware counters for profiling, such as PAPI [1] and Likwid [2]. In the future, hardware monitoring infrastructure will continue to play important roles, and that is why major processor companies are actively improving their on-chip hardware monitors to enhance user experience.

Designing hardware monitors to improve application performance is important, but we should also notice that there is significant demand for improving application power, energy and information leakage, as hardware platforms and software paradigms have rapidly changed in the past years. Today, programmers and system administrators not only care about performance, but also care about application power consumption, financial cost incurred by application energy consumption, and whether their applications run in a trustable system environment. Unfortunately, since existing hardware monitors were originally designed for just performance, they do not provide direct auditing support to the users about which parts of the program exhibit high power utilization, which program function consumes a lot of energy, and what process is leaking information over shared hardware resources. In response to such growing concerns, modern high performance processor architectures have begun integrating new counters for gathering processor power and energy usages. For example, starting from Sandy Bridge, Intel provides a driver interface called RAPL (Running Average Power Limit) that can let programmers periodically sample processor power/energy usually at the granularity of a few milliseconds of program execution time. While such counters could be used to obtain application power trace or total energy consumption, they do not provide feedback at a granularity that relates the processor power/energy consumption back to the program source code.

Therefore, we envision that the next generation multicore hardware monitoring infrastructure should provide better auditing support for application power, energy, and information leakage in an cost-effective manner, and ultimately, help programmers and system administrators to make actionable improvements.

## 1.2 Multicore Resource Usage Problems– Power, Energy, and Information Leakage

While the need for the next generation hardware monitoring infrastructure becomes clear, power, energy, and information leakage that resulted from applications' usage of hardware resources need to be understood better. In this section, we will review each resource usage problem.

Power has long been a design constraint in processors. Generations of processors used to follow Dennard scaling which states that, as transistors get smaller their power density stays constant, so that power stays constant as long as the dies size remains the same. While Dennard scaling starts to break down around 2005, the trend of integrating more number of cores has not been stopped. The consequence is that, due to limited power budget, only part of chip transistors can switch at full frequency, and many of them have to be powered off. As a result, software applications are forced to use only a portion of all the multi-core resources, for example, Intel Turbo Boost Mode runs half of the cores at full frequency, while shutting off the rest cores. Not appropriate usage of hardware resources may also trigger other power issues. As instances (1) An increase in the chip power density could affect the reliability of operation and result in decreased lifetime of processors [3], (2) Uneven consumption of power by different cores could complicate heat dissipation and electric supply in multicores [4]. As processor demands rapidly change the electric current consumption over a short timeframe, supply voltage perturbations could occur, resulting in power-delivery subsystem having large parasitic inductance and voltage ripples on the chip's supply lines. When voltage ripples exceed a certain tolerance range, CPUs may begin to malfunction [5]. Such unwanted consequences in applications can be mitigated by optimizing them for reduced peak power consumption, balancing power across different cores, and by minimizing the power density that can lead to thermal issues.

Energy is different from power in that it is the integral of power over time. Whenever a hardware resource is used, it just adds up to the energy cost. That being said, even after power has been optimized, application energy consumption, which directly translates to financial cost, does not get automatically reduced. Energy costs incurred by software applications have grown rapidly in recent years. In 2014, energy is projected to be a major expense for most major data centers, and is estimated to account for up to 3% of worlds total energy consumption [6]. However, not all applications are using hardware resources in an energy-efficient way. As instances– (1) unnecessary branches use branch units but the branch outcome never affects program execution. (2) redundant code repeatedly uses the processor pipeline but only for computing the same value. Because of that, Inefficient software has often been cited as a major reason for wasteful energy consumption in computing systems. To highlight the importance of application energy and its impact on data service efficiency, companies like eBay have online dashboards for the users to track energy consumption per transaction in their servers [7]. Such efforts clearly illustrate the motivation of major software giants in removing the inefficiencies in their applications.

While power and energy are two of the top issues in multi-core resource usages, there is a growing concern about information leakage on shared hardware resources. As processor core counts are increasing, more shared hardware resources are being integrated into the chip. For example, compute logics and execution engines are shared among virtual cores in processors that support SMT (Simultaneous Multithreading); the last level cache and the memory bus is shared among physical cores, etc. In recent years, it has been shown many times these shared resources are vulnerable one type of information leakage, namely, covert timing channels attacks. The inside malicious users can construct covert timing channels by intentionally modulating the timing of events on certain shared hardware resources to illegitimately reveal sensitive information to the outside world. Compared to software-based information leakage, hardware based approaches are mostly hidden and much harder to audit. As confinement mechanisms in software improve, such hardware-based information leakage are more likely to be exploited, and hence put the trust of systems at risk.

Currently, solving these resource usage problems on multicore hardware are of paramount importance. But, not having the right tools to address such problems just makes such tasks harder. Therefore, having the next generation hardware monitoring infrastructure to support auditing application power, energy and information leakage will greatly improve the productivity of programmers and system administers in addressing these new challenges.

## 1.3 Overview

This dissertation contains six chapters.

- Chapter 1 motivates the need for next generation hardware monitoring infrastructure for resource auditing, and states the reasons why the existing hardware infrastructure is not sufficient. It also briefly reviews power, energy, and information leakage problems resulted from the usage of processor hardware resources.

- Chapter 2 provides necessary background for this dissertation. We introduce specific problems in individual domains of application energy auditing, application power auditing, and covert timing channel auditing.

- Chapter 3 describes Watts-inside, a hardware-software cooperative approach for application power auditing. Watts-inside replies on the efficiency of hardware support to accurately gather application power profiles, and utilizes software support and causation principles for a more comprehensive understanding of application power.

- Chapter 4 describes enDebug, a hardware software cooperative framework for application energy auditing. EnDebug attributes energy consumption by applications to fine grain regions of program code (say functions), and utilizes an automated recommendation system to explore energy improvements in the program code.

- Chapter 5 describes CC-Hunter, a novel framework for covert timing channel auditing on shared hardware resources. CC-Hunter detects the presence of covert timing channels by dynamically tracking conflict patterns on shared processor hardware. It offers low-cost hardware support that gathers data on certain key indicator events during program execution, and provides software support to compute the likelihood of covert timing channels on a specific shared hardware.

- Chapter 6 presents conclusion of this work.

## **1.4** Scope of this Dissertation

The main goal of this work is to motivate the need for the next generation hardware infrastructure that is able to audit multicore resource usage problems, such as power, energy and information leakage. We describe our proposed solutions and the necessary hardware modifications to modern processors. We quantitatively evaluate our schemes either through simulators that model the modified processor platforms, or directly through real hardware machines where possible. For application power and energy auditing, we are interested in optimizing power or energy through code modifications. For information leakage auditing, we are interested in detecting covert timing channel activities on the shared hardware resources, rather than showing how to robustly construct these channels. Our work shows promising results that can be achieved from using application power, energy and information leakage auditing. We envision that this dissertation will stimulate more researches on improving the next generation hardware monitoring infrastructure to have further enhanced auditing capabilities that optimize applications for factors beyond just performance.

## Chapter 2

## Background

## 2.1 Application Power Auditing

Multicore processors have permeated the computing domains with their promise of higher performance and power efficiency over single core processors. With the limitations posed by Dennard scaling, power-related issues will be significant in future multicore chip designs and limit the scalability of multicore computing [8, 9, 10].

Conventional power saving strategies utilize dynamic, hardware-based solutions such as Dynamic Voltage-Frequency Scaling, Power and Clock Gating. Recent proposals have studied power management platforms that are either built as part of the the microprocessor circuitry [11, 12] or via tight interfacing with the external microcontrollers [13]. Unfortunately, such mechanisms are limited to dynamic power optimizations and can be cost-ineffective on applications that are not statically tuned for power. On the other hand, software-only power profiling tools are mostly disadvantaged by their limited knowledge of the underlying hardware parameters and complex interactions occurring between various functional units in multicore processors. Therefore, a more effective strategy is to combine the hardware efficiency in providing an accurate view of the program behavior with the software flexibility to effect low-cost, program-level power optimizations, ultimately improving the power

#### CHAPTER 2. BACKGROUND

consumption of multicore applications.

Our Watts-inside framework for power auditing combines the best of both hardware and software. The hardware performs power estimation and identifies the functional unit that was responsible for higher power in the captured code sequence. The software then does further analysis with finer grain code blocks (for instance, basic blocks) to figure out which region of program code was responsible for higher power.

Having information about specific code regions together with the functional units that are responsible for higher power, offers meaningful feedback to the users about how to apply power optimizations to the application. Such feedback can especially be more critical to heterogeneous multicore environment where the individual cores and the threads running on them have to be carefully tailored to maximize performance while reducing power. Our integrated approach to understanding multicore power can immensely aid in improving *application-level power awareness* and not just having to simply rely on the hardware-only mechanisms for power optimizations.

## 2.2 Application Energy Auditing

A plethora of solutions ranging from virtualization to application aware power management have been proposed to reduce system energy footprint. While such techniques are useful, a more effective solution is to incorporate energy smartness into the software itself such that the application performance can be aligned more closely with revenue. Being able to find the high energy consuming code region, and consequently, automate the process of energy optimization process would be vital to the future of energy-aware software development.

Conventionally, execution time of applications is a commonly adopted proxy measure for software developers to identify the energy bottlenecks in their program code. Recent studies by Hao et al [14] have shown that the execution time and energy consumption do not have a strong correlation because of several factors such as (1) multiple power states- at two different frequencies  $f_1$  and  $f_2$ , even if the execution times are the same, the energy drawn will be different, (2) asynchronous design of system and API calls- when the application sends data over the network, the data is handled by the OS which results in the corresponding datasending application not being charged for the data transmission time. These necessitate a dedicated framework for energy auditing.

Further, the application energy profile and optimizations are often specific to the processor architecture and hardware configurations. That is, a set of code optimizations that improve energy in one processor configuration does not necessarily improve the energy in other platforms. Without having a sound understanding of the underlying hardware details, many software-level energy models often resort to instruction-based or a specific hardware event-based (say, cache misses) energy accounting to derive application energy. Such strategies ignore the numerous and complex interactions between shared hardware resources and overlapped instruction execution that occur during application runtime. To overcome such problems, it is critical to debug the energy consumption of applications through profiles generated on the target architecture.

Our solution, enDebug, audits energy consumption by applications to fine grain regions of program code (say functions), and utilizes an automated recommendation system to explore energy improvements in the program code. In doing so, we enable the participation of software developers and toolchains (such as compilers and runtime) in energy-aware software development without necessarily having them to rely on expensive runtime energy saving strategies.

## 2.3 Information Leakage Auditing

Covert timing channels are information leakage channels where a trojan process intentionally modulates the timing of events on certain shared system resources to illegitimately reveal sensitive information to a spy process. Note that the trojan and the spy do not communicate explicitly through send/receive or shared memory, but via covertly modulating certain events (Figure 2.1). In contrast to side channels where a process unintentionally leaks information to a spy process, covert timing channels have an insider trojan process (with higher privileges) that intentionally colludes with a spy process (with lower privileges) to exfiltrate the system secrets.

Figure 2.1: A Covert Timing Channel using timing modulation on a shared resource to divulge secrets

To achieve covert timing based communication on shared processor hardware, a fundamental strategy used by the trojan process is modulating the timing of events through intentionally creating conflicts<sup>1</sup>. The spy process deciphers the secrets by observing the differences in resource access times. On hardware units such as compute logic and wires (buses/interconnects), the trojan creates conflicts by introducing distinguishable contention patterns on the shared resource. On caches, memory and disks, the trojan creates conflicts by intentionally replacing certain memory blocks such that the spy can decipher the message bits based on the memory hit/miss latencies. This basic strategy of creating conflicts for timing modulation has been observed in numerous covert timing channel implementations [15, 16, 17, 18, 19, 20, 21, 22, 23].

Recent studies [19, 22] show how popular computing environments like cloud computing are vulnerable to covert timing channels. Static techniques to eliminate timing channel attacks such as program code analyses are virtually impractical to enforce on every third-

$<sup>^{1}</sup>$ We use "conflict" to collectively denote methods that alter either the latency of a single event or the inter-event intervals.

party software, especially when most of these applications are available only as binaries. Also, adopting strict system usage policies (such as minimizing system-wide resource sharing or fuzzing the system clock to reduce the possibility of covert timing channels) could adversely affect the overall system performance. Our framework, CC-Hunter, audits the presence of covert timing channels by dynamically tracking conflict patterns on shared processor hardware. CC-Hunter offers low-cost hardware support that gathers data on certain key indicator events during program execution, and provides software support to compute the likelihood of covert timing channels on a specific shared hardware. CC-Hunter's dynamic detection is a desirable first step before adopting damage control strategies like limiting resource sharing or bandwidth reduction. As a lightweight detection framework that audits on-chip hardware resources, our framework can be extremely beneficial to users as we transition to an era of running our applications on remote servers that host programs from many different users.

## Chapter 3

## Watts-inside: Application Power Auditing

## 3.1 Motivation – Understanding Multicore Power

To understand the power consumption behavior of applications, we perform experiments that characterize their power when executing on symmetric multicore processors. We note that more complex multicore environments that are asymmetric or heterogeneous can present even further challenges. In our studies, we run four-threaded applications on four core processors without placing any specific constraints on power consumption or voltage-frequency settings, i.e., the settings are assumed to result in the best possible execution time. We measure chipwide power during intervals of 10,000 cycles by running our benchmarks on SESC [24], a cycle-accurate architecture simulator with an integrated dynamic power model that uses Wattch [25] and Cacti [26] for power estimation. 32 nm technology is assumed in all of our experiments. Figure 3.1 shows dynamic power traces for a representative subset of our benchmark applications when executing on four-core processors. Our results indicate that different multicore applications can exhibit different characteristics during the various phases of their execution– (1) monotonically increasing power, e.g., cholesky, (2) phases of high and low power, e.g., ocean, (3) occasional peaks of high power, e.g., volrend, and (4) almost uniform power, e.g., fluidanimate.

Figure 3.1: Dynamic Power traces for four-threaded applications measured during their execution

Even for applications that have been thoroughly debugged for performance and load balanced, our studies show that the parallel sections of multicore applications could still suffer from uneven power consumption between multiple cores. Table 3.1 shows parallel sections in some of the well-known Splash-2 and Parsec-1.0 applications that are running on four cores with four threads and shows the average imbalance in performance and power across several dynamic instances of the parallel section. Note that average power (or performance) imbalance in an application's parallel section is measured as the average difference between the threads having the highest and lowest power (or execution time). Despite almost perfect performance balance that can be achieved through hardware optimizations like out-of-order execution and prefetching, we see significant power imbalance (up to 31.7% in cholesky) across the different cores because power consumption by the functional units are still deter-

Table 3.1: Performance and Dynamic Power imbalance in SPLASH-2 and PARSEC-1.0 benchmarks with four threads

| Application  | Parallel               | Num. of   | % of Application | Average     | Average   |

|--------------|------------------------|-----------|------------------|-------------|-----------|

|              | Section                | Dynamic   | Execution        | Performance | Power     |

|              | (File/Function)        | Instances | Time             | Imbalance   | Imbalance |

| Volrend      | adaptive.c/ray_trace() | 3         | 44.33%           | 0.001%      | 10.21%    |

| (SPLASH-2)   |                        |           |                  |             |           |

| Barnes       | load.C/maketree()      | 4         | 72.47%           | 0.90%       | 8.89%     |

| (SPLASH-2)   |                        |           |                  |             |           |

| Cholesky     | solve.C/Go()           | 1         | 28.09%           | 2.82%       | 31.74%    |

| (SPLASH-2)   |                        |           |                  |             |           |

| Bodytrack    | WorkerGroup.cpp/       | 82        | 50.06%           | 0.47%       | 4.32%     |

| (PARSEC-1.0) | WorkerGroup::Run()     |           |                  |             |           |

mined by the amount of work to be done. These results are consistent with a recent survey by Chen et al [27] and show the necessity to understand the application's power characteristics in greater detail in order to accurately effect changes that improve power consumption.

## 3.2 Design Overview

### 3.2.1 Hardware Support

To improve power, the user (programmer, compiler or the hardware) should first understand which parts of the program code suffer from power-related issues and what functional units are responsible for this effect. We design hardware support that estimates dynamic power for a string of N consecutively executing basic blocks (which we call Code Sequence), and log its power information in memory for further analysis. A code sequence is chosen as a granularity in our hardware design to capture meaningful power information that is relatable back to program code, while minimizing the hardware implementation complexity. In our

Figure 3.2: Design overview of the Watts-inside framework

experiments, we assume N=5 because it offers a nice trade-off between capturing power information at finer granularity and accuracy of power measurement on overlapped instructions. Sometimes, a code sequence can contain fewer than N basic blocks in cases of a function call/return and exceptions; we terminate such code sequences prematurely to prevent them from straddling program function boundaries and exceptions.

Figure 3.2 depicts an overview of our hardware-software design for Watts-inside framework. Conceptually, we divide the hardware support for Watts-inside into three stages, namely,

#### **Power Estimator**

This module is responsible for computing (or estimating) the power consumption of code sequences. The processor chip is embedded with activity sense points inside various functional units which are monitored by a power estimator unit. In our design, this module is conceptually similar to the IBM Power7's power proxy module that has specifically architected and programmably weighted counter-based architecture to keep track of activities and form an aggregate value denoting power [13].

#### **Adaptive Filter**

This module is responsible for filtering code sequences that are essentially 'uninteresting' with respect to power and do not warrant a *second hardware-level* analysis for functional unitspecific power information. Note that, when needed, the software profiler has the capability to analyze all code sequences regardless of filtering.

The adaptive filter has two active parameters– (1) maximum power so far (observed from the start of the application execution), and (2) capture ratio (C), a user-defined parameter that specifies the threshold for code sequences whose average power fall within the top C% of highest power (e.g., if the capture ratio is 10% and the highest power for any code sequence so far is 50 W, then the filter forwards all of the code sequences whose power consumption is at least 45 W.). In the remaining sections of this Chapter, we refer to high power code sequences as ones within the capture ratio, and the remaining code sequences as low power (or NOT high power) for simplicity.

To detect the high power sequences, the filter checks whether the code sequence (Q's) power falls within or exceeds the high power range. If true, then the filter forwards Q to the Power Analyzer for further processing. Whenever Q's power exceeds the maximum power observed thus far in the application, maximum power and threshold are updated. We note that after the maximum power reaches a stable value (i.e., after the highest power consuming sequence has executed), updates are no longer necessary.

#### **Power Analyzer**

This module is responsible for estimating the contribution of individual microarchitectural (or functional) units for high power code sequences, and then determining the functional unit that was responsible for the highest amount of power. We forward the output of this stage to a log that can be further analyzed by software profilers.

| Code Sequence ID | Power  | Core<br>ID | Execution<br>Time | FU ID  | FU<br>Power |

|------------------|--------|------------|-------------------|--------|-------------|

| L                |        |            |                   |        |             |

| 64 bits          | 7 bits | 5 bits     | 9 bits            | 4 bits | 7 bits      |

Figure 3.3: Code Sequence Power Profile Vector (CSPPV)

For design efficiency, we adopt common activity based component power estimation that can estimate power for a large number of functional units using just a few generic performance counters [28]. We identify fourteen functional units (Instruction and Data Translation Lookaside Buffers, Instruction and Data Level-1 caches, Branch Predictor, Rename logic, Reorder Buffer, Register File, Scheduler, Integer ALU, Float ALU, Level-2 cache, Level-3 cache and Load Store Queue) to study the power breakdown by individual units . We chose these fourteen units based on our analysis of functional unit-level power consumption across our benchmark suites.

Figure 3.3 shows the output of the Watts-inside hardware. For each code sequence, we construct a 96-bit long Code Sequence Power Profile Vector (CSPPV) that includes:

• Code Sequence ID: The power estimator generates a unique 64-bit identifier for every code sequence by folding the 32-bit address of the first basic block, and then concatenating lower order bits of other constituent basic blocks within the code sequence.

• Code Sequence Power: The power estimator uses 7 bits to store the code sequence power.

• Core ID: 5 bits are used for the core ID where the code sequence executed, filled by power estimator.

• Execution time: The power estimator uses 9 bits to store the execution time of the code sequence. This can be later used for: (1) computing energy, and (2) ranking code sequences to prioritize longer running blocks.

• FU ID: The power analyzer uses 4 bits to uniquely identify the one of the fourteen

functional units that consumes the most power.

• FU Power: The power analyzer uses 7 bits to show power consumed by the highest power consuming functional unit.

The power analyzer module records the CSPPV into a memory log that can later be utilized by software profilers.

### 3.2.2 Software Support

#### Causation probability

To help programmers and compilers apply targeted power-related optimizations to program code, feedback must be given at the level of fine-grain code blocks (say, a few instructions within a basic block). Toward this goal, we develop a causation probability model to determine whether an individual basic block within a code sequence could cause higher power.

Watts-inside quantifies the impact of a certain basic block B on the power of the code sequence Q using three probability metrics:

- Probability of Sufficiency (PS): If B is present, then Q consumes high power. A higher range of PS values indicate that the presence of B is a sufficient cause for Q's high power consumption.

- Probability of Necessity (PN): Among Qs that consume high power, if B were not present, then Q would have not consumed high power. A higher range of PN values indicate that the absence of B would have caused Q to lower its power.

- Probability of Necessity and Sufficiency (PNS): B's presence is both sufficient and necessary to infer that Q consumes high power. Higher values of PNS prove that B's likeliness to be the reason behind Q's higher power.

To compute the boundaries of PS, PN and PNS, we define the following additional probability terms:

Let b be the event that a basic block B occurs in a code sequence, and h be the event that the code sequence consumes high power.  $P(h_b)$  denotes counterfactual relationship between b and h, i.e., the probability that if b had occurred, h would have been true.

$$P(h) = (\#HighPowerSeq)/(\#Seq)$$

(3.1)

$$P(b,h) = (\#HighPowerSeqWithB)/(\#Seq)$$

(3.2)

$$P(b', h') = (\#LowPowerSeqWithoutB)/(\#Seq)$$

(3.3)

$$P(h_b) = (\#HighPowerSeqWithB) / (\#SeqWithB)$$

(3.4)

$$P(h_{b'}) = (\#HighPowerSeqWithoutB) / (\#SeqWithoutB)$$

$$(3.5)$$

$$P(h'_{b'}) = (\#LowPowerSeqWithoutB) / (\#SeqWithoutB)$$

(3.6)

The boundary values for PS, PN and PNS are defined below:

$$max\left\{0, \frac{P(h_b) - P(h)}{P(b', h')}\right\} \le PS \le min\left\{1, \frac{P(h_b) - P(b, h)}{P(b', h')}\right\}$$

(3.7)

$$max\left\{0, \frac{P(h) - P(h_{b'})}{P(b, h)}\right\} \le PN \le min\left\{1, \frac{P(h'_{b'}) - P(b', h')}{P(b, h)}\right\}$$

(3.8)

$$PNS \ge max \left\{ \begin{array}{l} 0, P(h_b) - P(h_{b'}), \\ P(h) - P(h_{b'}), P(h_b) - P(h) \end{array} \right\}$$

(3.9)

$$PNS \le min \left\{ \begin{array}{l} P(h_b), P(h'_{b'}), P(b,h) + P(b',h'), \\ P(h_b) - P(h_{b'}) + P(b,h') + P(b',h) \end{array} \right\}$$

(3.10)

By using the boundary equations 3.7- 3.10, we present a few test cases below to verify our causation model:

• If a basic block B appears frequently in high power code sequences and sparsely in low power sequences, both PS and PN boundary values are very high (closer to 1.0). Consequently, PNS values are also very high. Such blocks *are certainly* candidates for power optimization. For example, if there are 1000 code sequences, of which 200 are classified as high power (via capture ratio C). Let us assume that  $B_1$  appears in 100 of the high power code sequences, and does not appear in any low power sequences. Using the boundary equations, we find that  $1 \leq PS \leq 1$  and  $0.9 \leq PN \leq 1$ . These high PS and PN values show that  $B_1$  is certainly a candidate for power optimizations.

• If a basic block B appears sparsely in high power code sequences, both PS boundary values are closer to 0.0, and the PN boundary values are either a widely varying range or are closer to 0.0. Such blocks *cannot* be good candidates for power improvement considerations. Using the same example above, let us assume that the block  $B_2$  appears in 5 of the 200 high power code sequences and  $B_2$  appears in 95 of the 800 low power (NOT high power) code sequences. Using the boundary equations, we find that  $0 \leq PS \leq 0.06$  and  $0 \leq PN \leq 1$ . Low PS values combined with practically unbounded PN values indicate that  $B_2$  cannot be a good candidate for power improvement.

• If a basic block B appears L% of the time in high power code sequences and M% of the time in low power sequences (where L and M are non-trivial), PNS boundary values determine the degree to which B's likeliness in causing higher power in the corresponding program code sequences. Therefore, higher ranges of PNS values for B indicates higher benefit in applying power-related optimizations to B. Using the example described above, let us consider two blocks  $B_3$  and  $B_4$ - (1)  $B_3$  appears in 40 of the 200 high power code sequences and in 200 of the 800 low power code sequences, where  $0 \le PNS \le 0.167$ , and (2)  $B_4$  appears in 35 of the 200 high power sequences and 20 of the 800 low power sequences, where  $0.462 \le PNS \le 0.636$ . Even though  $B_3$  appears more frequently in high power code sequences than  $B_4$ , there is higher benefit to optimizing  $B_4$  because of its *larger* high power causation probability.

We find that this approach mathematically helps us to quantify the degree to which a specific set of instructions result in higher power consumption.

#### Code Sequences with varying power consumption between cores

Our software support can improve the quality of feedback information via two mechanisms -(1) Use clustering algorithms (e.g., k-means) to cluster sequences based on the degree of power variation, i.e., code sequences that show higher power variation are clustered separately from the ones that have lower power variation. This can aid runtime systems to do better scheduling of threads and map them on to cores that satisfy their power needs. (2) Identify the cause for power variation using the CSPPVs. Since the vector contains information on functional unit consuming the highest power, it can facilitate targeted optimizations including code changes and dynamic recompilation.

#### Predicting potential for Thermal Hotspots

By monitoring a contiguous stream of code sequences executing on the same core where a functional unit repeatedly contributes to the highest portion of power, we could predict parts of the chip where thermal hotspots could develop. Also, by having information on the physical chip floorplan, we can even detect local thermal hotspots resulting out of continuously high activity in adjacent functional units. Such analysis can effectively help temperatureaware software development of multicore applications.

## 3.3 Implementation

In this section, we show how our framework can be integrated with a modern multicore architecture.

### 3.3.1 Hardware Support

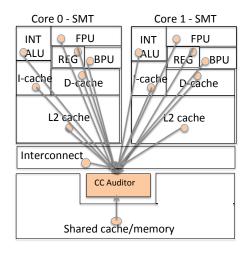

Figure 5.8 shows the hardware modifications needed to implement Watts-inside framework. We include the power estimator (similar to the modules found in modern processors like Intel Sandybridge, IBM Power7) and adaptive filter logic locally in every core. After power

Figure 3.4: Hardware modifications needed for Watts-inside framework

estimation, our adaptive filter determines whether this block warrants further processing. To do this, there are two special registers- a programmable register to store the user-desired capture ratio, and an internal register to hold maximum power observed so far.

We implement the power analyzer module as a centralized resource that is shared by all cores within a multicore chip. The adaptive filters inside the cores forward only the high power code sequences to the power analyzer.

To reduce the performance impact of hardware profiling, we consider two more optimizations– (1) hardware buffer to accumulate the CSPPVs and update memory when the bus is idle, and (2) sampling of code sequences to minimize the impact on multicore performance.

Additionally, we implement an online hardware causation probability module and a watch register (that can be programmed by the user with a specific basic block address). This is conceptually similar to setting watchpoints in program debuggers. The adaptive filter forwards all of the code sequences that contains the *basic block address under watch* to the hardware causation probability module, that in turn computes the PS, PN and PNS values. We believe that such a feature shall aid runtime systems like dynamic recompilation or adaptive schedulers to optimize specific code regions during program execution.

### 3.3.2 Software Support

We run the software profiler as a separate privileged process in the kernel mode. The profiler supports APIs for functions such as (1) querying which basic blocks have high power causation probability (note: this offline software implementation is more comprehensive and separate from the online hardware causation probability module in Section 3.3.1), (2) automatically mining the CSPPVs for basic blocks that cause higher power. This software profiler gets its input from the CSPPV log created by the power analyzer. The memory pages belonging to CSPPV log are managed by the Operating System and are allocated on demand. If the OS senses that memory demands of CSPPV log interferes with the performance of regular applications, the OS pre-emptively deallocates certain memory pages and/or alter the sampling rate of code sequences to minimize the memory demands of CSPPV logs [29], that helps us to reduce memory footprint sizes.

### 3.4 Experimental Setup

We use SESC, a cycle accurate architectural multicore simulator [24] that has an integrated power model. We model a four-core Intel Core i7-like processor [30] running at 3 GHz, 4-way, out-of-order core, each with a private 32 KB, 8-way associative Level 1 cache and a private 256 KB, 8-way associative Level 2 cache. All cores share a 16 MB, 16-way set-associative Level 3 cache. The Level 2 caches are kept coherent using the MESI protocol. The block size is assumed to be 64 Bytes in all caches. We use parallel applications from Splash-2 [31] and PARSEC-1.0 [32] that were compiled by gcc with -O3 flag, and run four-threaded version on

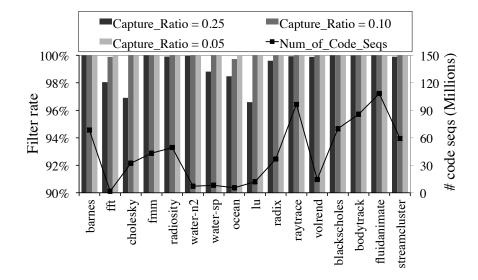

Figure 3.5: Ideal Filter rate for capture ratios of 0.25, 0.1 and 0.05. The right axis shows the number of code sequences that are executed across all four threads.

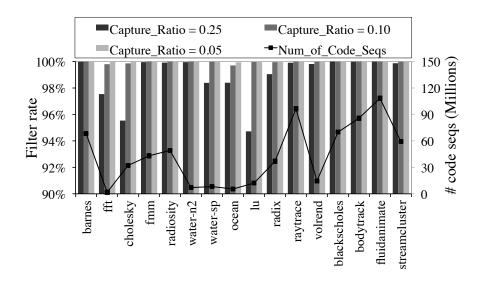

Figure 3.6: Adaptive Filter rate for capture ratios of 0.25, 0.1 and 0.05. The right axis shows the number of code sequences that are executed across all four threads.

four cores.

## 3.5 Evaluation

### 3.5.1 Adaptive Filter vs. Ideal Filter

In this experiment, we compare the effectiveness of our adaptive filter (that *adjusts its threshold dynamically* to filter code sequences based on the maximum power seen thus far and the capture ratio) against an ideal filter (that *does not need to adjust the threshold dynamically* because it has prior knowledge of the maximum power consumed by any code sequence in the multicore application and the capture ratio). Figures 3.5 and 3.6 show the results of our experiments. For each benchmark, we show the percentage of code sequences that are filtered for three separate capture ratios namely 0.25 (or code sequences within top 25% of maximum power), 0.10 and 0.05 respectively. On the right axis, we show the total number of code sequences that are executed by each application. As an example, cholesky benchmark executes a total of 32.13 million code sequences; at a capture ratio of 0.25, 96.9% of the code sequences are filtered by ideal filter and 95.5% of the code sequences are filtered by ideal filter and 95.5% of the code sequences are filtered by adaptive filter.

Based on our experiments, we notice that in a majority of benchmarks, except fft, cholesky and lu, our adaptive filter successfully filters above 99% of the code sequences (for all three capture ratios) and sends only  $\leq 1\%$  code sequences to the power analyzer module for further analysis. These filter rates are nearly same as that of the ideal filter. In fluidanimate that has a large number of code sequences, our adaptive filter performs nearly equal to the ideal filter in minimizing the number of sequences that are sent to the Power Analyzer. In certain benchmarks like lu, our adaptive design filters up to 3.8% less than an ideal filter, especially for capture ratio of 0.25. However, lu has fewer than 12 million code sequences and the absolute numbers of code sequences that reach power analysis stage are still far fewer than the benchmarks with hundreds of millions of code sequences. Therefore, we conclude that

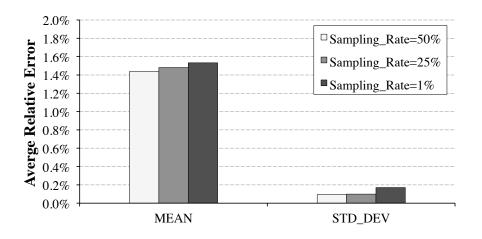

Figure 3.7: Average relative error in the mean and standard deviation of power consumption by code sequences (in Splash-2 and Parsec-1.0 applications) due to sampling, relative to a baseline execution without sampling.

our adaptive filter design proves effective and is able to perform very close to an ideal filter.

### 3.5.2 Sampling

Even after filtering, for certain applications, the number of CSPPVs might still be high enough to cause significant performance overheads. To minimize the traffic of code sequences that reach the power analyzer module from various cores, we perform periodic sampling, i.e, one out of every N code sequences is chosen by Watts-inside framework for power estimation and analysis. Figure 3.7 shows the results of our experiments when we sample code sequences at the rates of 50%, 25% and 1%, and compare the observed mean and standard deviation of code sequence power with the baseline execution where we do not have sampling. At 50%, we note that periodic sampling introduces fairly low relative error of about 1.4% on mean code sequence power and approximately 0.10% on standard deviation; at lower sampling rates, these relative errors are slightly worse. One caveat with aggressive sampling (such as 1%) is that we might only see fewer CSPPV samples, that may result in inability to accurately assess PNS, PS and PN probability values for certain basic blocks that are omitted due to

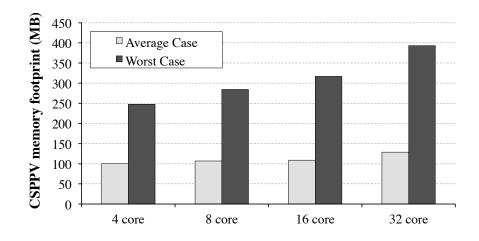

Figure 3.8: Average and worst-case CSPPV Memory log requirements for capture ratio=0.25 for different numbers of cores

sampling.

## 3.5.3 Scalability of CSPPV Memory Log