|                                  | Model    | Power 5                            |

|----------------------------------|----------|------------------------------------|

| Instructions Issued<br>per clock | Infinite | 4                                  |

| Instruction Window<br>Size       | Infinite | 200                                |

| Renaming<br>Registers            | Infinite | 88 integer +<br>88 Fl. Pt.         |

| Branch Prediction                | Perfect  | 2% to 6% misprediction             |

|                                  |          | (Tournament<br>Branch Predictor)   |

| Cache                            | Perfect  | 64KI, 32KD, 1.92MB<br>L2, 36 MB L3 |

| Memory Alias<br>Analysis         | Perfect  | ??                                 |

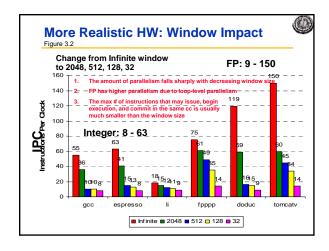

| Limit                               | Limits to ILP HW Model comp   |          |                                    |  |

|-------------------------------------|-------------------------------|----------|------------------------------------|--|

|                                     | New Model                     | Model    | Power 5                            |  |

| Instructions<br>Issued per<br>clock | Infinite                      | Infinite | 4                                  |  |

| Instruction<br>Window Size          | Infinite, 2K, 512,<br>128, 32 | Infinite | 200                                |  |

| Renaming<br>Registers               | Infinite                      | Infinite | 88 integer +<br>88 Fl. Pt.         |  |

| Branch<br>Prediction                | Perfect                       | Perfect  | 2% to 6%<br>misprediction          |  |

|                                     |                               |          | (Tournament Branch<br>Predictor)   |  |

| Cache                               | Perfect                       | Perfect  | 64KI, 32KD, 1.92MB<br>L2, 36 MB L3 |  |

| Memory<br>Alias                     | Perfect                       | Perfect  | ??                                 |  |

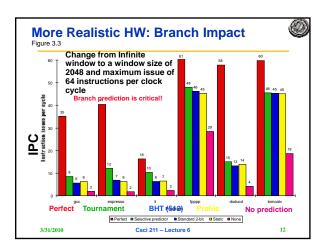

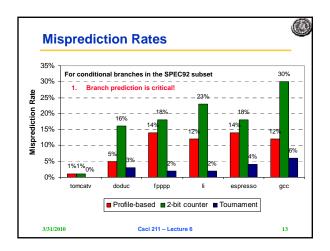

| Limits to ILP HW Model comparison   |                                                                       |                             |                                                               |  |

|-------------------------------------|-----------------------------------------------------------------------|-----------------------------|---------------------------------------------------------------|--|

|                                     | New Model                                                             | Model                       | Power 5                                                       |  |

| Instructions<br>Issued per<br>clock | 64 10 times as larg                                                   | Infinite<br>ger as the best | 4<br>implementation in 2005                                   |  |

| Instruction<br>Window Size          | 2048                                                                  | Infinite                    | 200                                                           |  |

| Renaming<br>Registers               | Infinite                                                              | Infinite                    | 88 integer +<br>88 Fl. Pt.                                    |  |

| Branch<br>Prediction                | Perfect vs. 8K<br>Tournament vs.<br>512 2-bit vs.<br>profile vs. none | Perfect                     | 2% to 6%<br>misprediction<br>(Tournament Branch<br>Predictor) |  |

| Cache                               | Perfect                                                               | Perfect                     | 64KI, 32KD, 1.92MB<br>L2, 36 MB L3                            |  |

| Memory<br>Alias                     | Perfect                                                               | Perfect                     | ??                                                            |  |

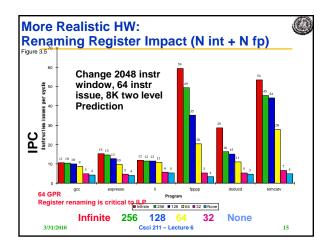

|                                     | New Model                             | Model    | Power 5                            |  |

|-------------------------------------|---------------------------------------|----------|------------------------------------|--|

| Instructions<br>Issued per<br>clock | 64                                    | Infinite | 4                                  |  |

| Instruction<br>Window Size          | 2048                                  | Infinite | 200                                |  |

| Renaming<br>Registers               | Infinite v. 256,<br>128, 64, 32, none | Infinite | 88 integer +<br>88 Fl. Pt.         |  |

| Branch<br>Prediction                | 8K two level<br>tournament            | Perfect  | Tournament Branch<br>Predictor     |  |

| Cache                               | Perfect                               | Perfect  | 64KI, 32KD, 1.92MB<br>L2, 36 MB L3 |  |

| Memory<br>Alias                     | Perfect                               | Perfect  | Perfect                            |  |

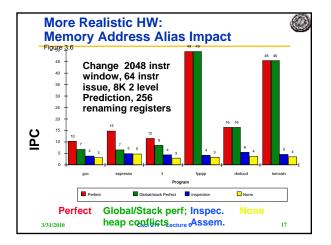

|                                     | New Model                                 | Model    | Power 5                            |  |

|-------------------------------------|-------------------------------------------|----------|------------------------------------|--|

| Instructions<br>Issued per<br>clock | 64                                        | Infinite | 4                                  |  |

| Instruction<br>Window Size          | 2048                                      | Infinite | 200                                |  |

| Renaming<br>Registers               | 256 Int + 256 FP                          | Infinite | 88 integer +<br>88 Fl. Pt.         |  |

| Branch<br>Prediction                | 8K two level<br>tournament                | Perfect  | Tournament                         |  |

| Cache                               | Perfect                                   | Perfect  | 64KI, 32KD, 1.92MB<br>L2, 36 MB L3 |  |

| Memory<br>Alias                     | Perfect v. Stack<br>v. Inspect v.<br>none | Perfect  | Perfect                            |  |

(TR)

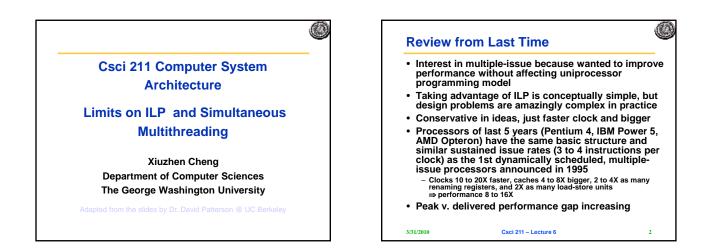

Csci 211 – Lecture 6

3/31/2010

(U)

25

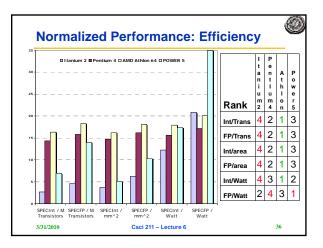

| Processor                        | Micro architecture                                                | Fetch /<br>Issue /<br>Execute | FU             | Clock<br>Rate<br>(GHz) | Transis<br>-tors<br>Die size              | Power         |

|----------------------------------|-------------------------------------------------------------------|-------------------------------|----------------|------------------------|-------------------------------------------|---------------|

| Intel<br>Pentium<br>4<br>Extreme | Speculative<br>dynamically<br>scheduled; deeply<br>pipelined; SMT | 3/3/4                         | 7 int.<br>1 FP | 3.8                    | 125 M<br>122<br>mm <sup>2</sup>           | 115<br>W      |

| AMD<br>Athion 64<br>FX-57        | Speculative<br>dynamically<br>scheduled                           | 3/3/4                         | 6 int.<br>3 FP | 2.8                    | 114 M<br>115<br>mm <sup>2</sup>           | 104<br>W      |

| IBM<br>Power5<br>(1 CPU<br>only) | Speculative<br>dynamically<br>scheduled; SMT;<br>2 CPU cores/chip | 8/4/8                         | 6 int.<br>2 FP | 1.9                    | 200 M<br>300<br>mm <sup>2</sup><br>(est.) | 80W<br>(est.) |

| Intel<br>Itanium 2               | Statically<br>scheduled<br>VLIW-style                             | 6/5/11                        | 9 int.<br>2 FP | 1.6                    | 592 M<br>423<br>mm <sup>2</sup>           | 130<br>W      |