| ⇒ any chang                        | cception behavior<br>es in instruction execution order<br>nge how exceptions are raised in<br>cceptions) |

|------------------------------------|----------------------------------------------------------------------------------------------------------|

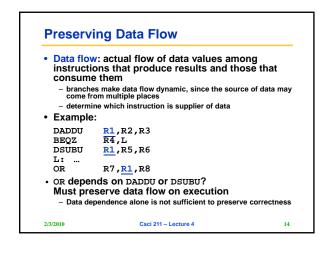

| • Example:                         | . ,                                                                                                      |

| DADDU                              | R2,R3,R4                                                                                                 |

| BEQZ                               | R2,L1                                                                                                    |

| LW                                 | R1,0(R2) ;no data dependences                                                                            |

| between BEQZ                       | and LW                                                                                                   |

| L1:                                |                                                                                                          |

| <ul> <li>– (Assume bran</li> </ul> | ches not delayed)                                                                                        |

|                                    | moving LW before BEQZ?                                                                                   |

|                                    |                                                                                                          |

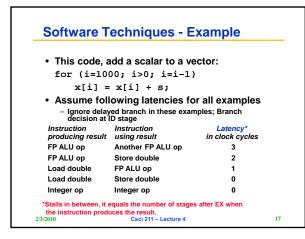

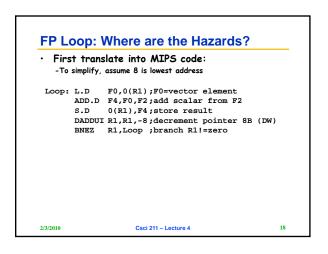

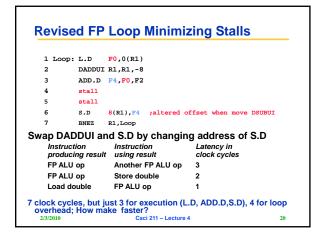

| LL L                  | loop   | Snowi                   | ng Stal    | IS                         |

|-----------------------|--------|-------------------------|------------|----------------------------|

| 1 Loop:               | L.D    | F0,0(R1)                | ;F0=vecto  | r element                  |

| 2                     | stall  |                         |            |                            |

| 3                     | ADD.D  | <b>F4,F0,F</b> 2        | ;add scala | ar in F2                   |

| 4                     | stall  |                         |            |                            |

| 5                     | stall  |                         |            |                            |

| 6                     | s.D    | 0(R1), <mark>F4</mark>  | ;store rea | sult                       |

| 7                     | DADDUI | R1,R1,-8                | ;decrement | t pointer 8B (DW)          |

| 8                     | stall  |                         | ;assumes d | an't forward to brand      |

| 9                     | BNEZ   | R1,Loop                 | ;branch R  | L!=zero                    |

| Instructi<br>producir | ••••   | Instructio<br>using res |            | Latency in<br>clock cycles |

| FP ALU (              | ор     | Another F               | P ALU op   | 3                          |

| FP ALU (              | ор     | Store dou               | ble        | 2                          |

| Load do               | uble   | FP ALU o                | р          | 1                          |

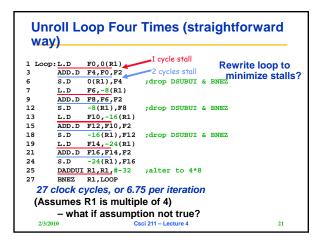

| 1 L | oop:L.D    | F0,0(R1)                   |  |

|-----|------------|----------------------------|--|

| 2   | L.D        | F6,-8(R1)                  |  |

| 3   | L.D        | F10,-16(R1)                |  |

| 4   | L.D        | F14,-24(R1)                |  |

| 5   | ADD.D      | F4,F0,F2                   |  |

| 6   | ADD.D      | F8,F6,F2                   |  |

| 7   | ADD.D      | F12,F10,F2                 |  |

| 8   | ADD.D      | F16,F14,F2                 |  |

| 9   | S.D        | 0(R1),F4                   |  |

| 10  | S.D        | -8(R1),F8                  |  |

| 11  | S.D        | -16(R1),F12                |  |

| 12  | DSUBUI     | R1,R1,#32                  |  |

| 13  | S.D        | 8(R1),F16 ; 8-32 = -24     |  |

| 14  | BNEZ       | R1,LOOP                    |  |

| 1   | A clock cu | cles, or 3.5 per iteration |  |

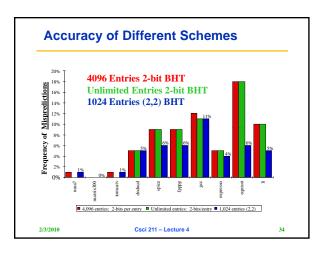

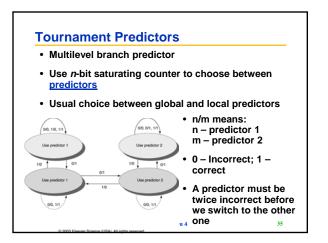

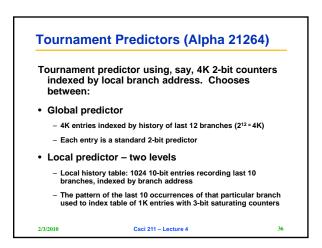

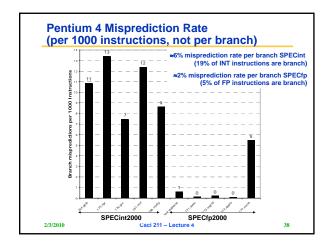

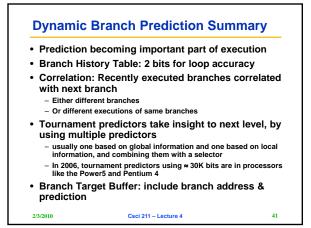

| <ul> <li>Particularly crucial for integer benchmarks.</li> <li>A typical tournament predictor will select the global p<br/>almost 40% of the time for the SPEC integer benchmark<br/>less than 15% of the time for the SPEC FP benchmark.</li> </ul> |                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| almost 40% of the time for the SPEC integer benchma                                                                                                                                                                                                  |                      |

| 8% r                                                                                                                                                                                                                                                 | S                    |

| 5°                                                                                                                                                                                                                                                   |                      |

|                                                                                                                                                                                                                                                      | cal 2-bit predictors |

| 59                                                                                                                                                                                                                                                   |                      |

| Conditional branch 4%                                                                                                                                                                                                                                |                      |

|                                                                                                                                                                                                                                                      | relating predictors  |

| 26                                                                                                                                                                                                                                                   | marrient predictors  |

|                                                                                                                                                                                                                                                      |                      |

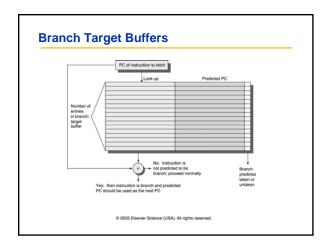

## **Branch Target Buffers (BTB)**

- Branch target calculation is costly and stalls the instruction fetch.

- BTB stores PCs the same way as caches

- The PC of a branch is sent to the BTB

- When a match is found the corresponding Predicted PC is returned

- If the branch was predicted taken, instruction fetch continues at the returned predicted PC

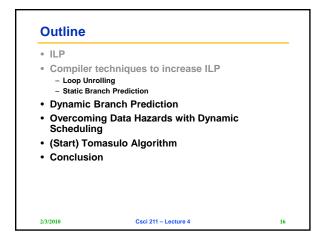

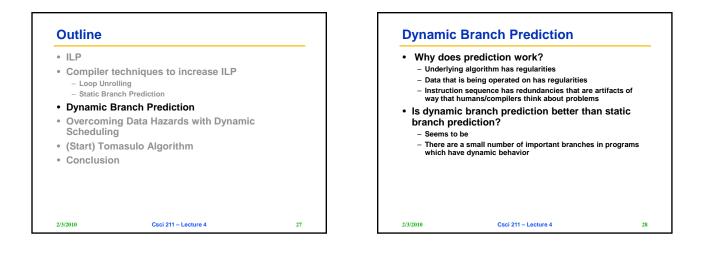

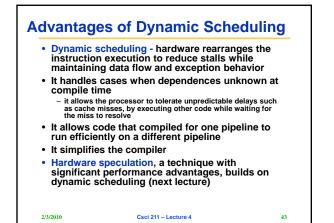

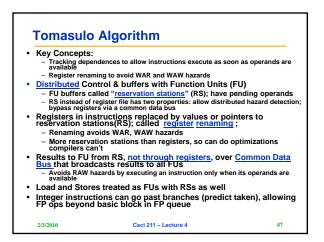

## Outline

- ILP

- Compiler techniques to increase ILP

Loop Unrolling

Static Branch Prediction

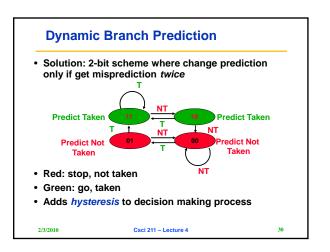

- Dynamic Branch Prediction

- Overcoming Data Hazards with Dynamic Scheduling

– (Start) Tomasulo Algorithm

Csci 211 – Lecture 4

Conclusion

2/3/2010

42

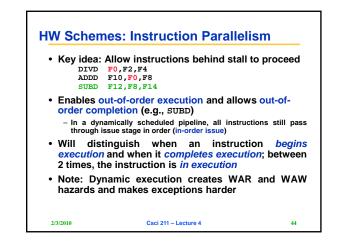

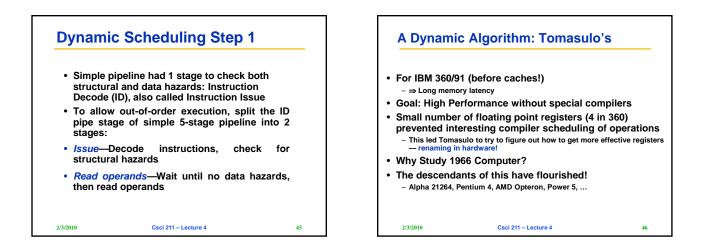

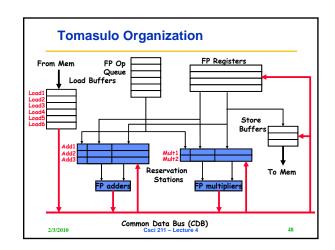

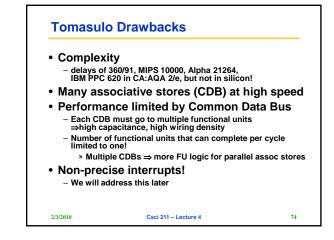

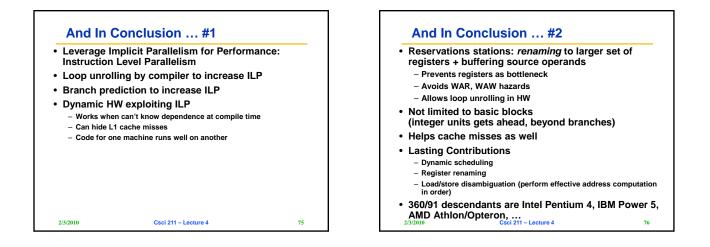

## Tomasulo's scheme offers 2 major advantages

- 1. Distribution of the hazard detection logic

- distributed reservation stations and the CDB

- If multiple instructions waiting on single result, & each instruction has other operand, then instructions can be released simultaneously by broadcast on CDB

- If a centralized register file were used, the units would have to read their results from the registers when register buses are available

- 2. Elimination of stalls for WAW and WAR hazards

2/3/2010

Csci 211 – Lecture 4

73