### Direct-Mapped Cache (1/2)

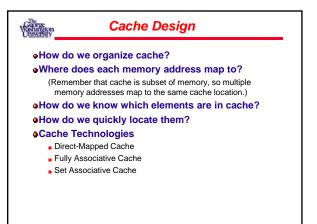

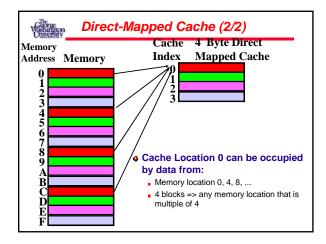

- In a <u>direct-mapped cache</u>, each memory address is associated with one possible <u>block</u> within the cache

- Therefore, we only need to look in a single location in the cache for the data if it exists in the cache

- Block is the unit of transfer between cache and memory

| Issues with D                                                                                                                                  | irect-Mapped                      | d                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------|

| <ul> <li>Since multiple memory ac<br/>cache index, how do we to</li> <li>What if we have a block s</li> <li>Answer: divide memory a</li> </ul> | ell which one is<br>ize > 1 byte? | in there?                         |

| ttttttttttttt                                                                                                                                  | iiiiiiiii                         | 0000                              |

| tag<br>to check<br>if have<br>correct block                                                                                                    | index<br>to<br>select<br>block    | byte<br>offset<br>within<br>block |

- •All fields are read as unsigned integers.

- Index: specifies the cache index (which "row" of the cache we should look in)

- <u>Offset</u>: once we've found correct block, specifies which byte within the block we want

- Tag: the remaining bits after offset and index are determined; these are used to distinguish between all the memory addresses that map to the same location

### Direct-Mapped Cache Example (1/3)

- Suppose we have a 16KB of data in a direct-mapped cache with 4 word blocks

- Determine the size of the tag, index and offset fields if we're using a 32-bit architecture

#### Offset

- need to specify correct byte within a block

- block contains 4 words

= 16 bytes = 2<sup>4</sup> bytes

need 4 bits to specify correct byte

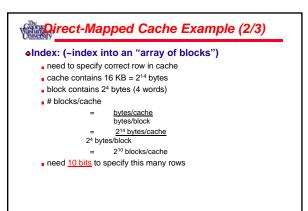

## Direct-Mapped Cache Example (3/3)

### •Tag: use remaining bits as tag

tag length = addr length – offset - index = 32 - 4 - 10 bits

= 18 bits

so tag is leftmost 18 bits of memory address

### •Why not full 32 bit address as tag?

- All bytes within block need same address (4 bits)

- Index must be same for every address within a block, so it's redundant in tag check, thus can leave off to save memory (here 10 bits)

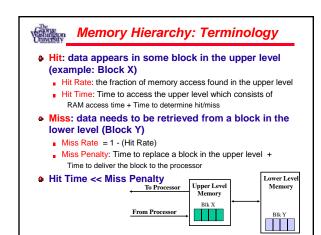

#### Wishington University Caching Terminology When we try to read memory, 3 things can happen: • cache hit: 1. cache block is valid and contains proper address, so read desired word cache miss: 2. nothing in cache in appropriate block, so fetch from memory cache miss, block replacement: 3. wrong data is in cache at appropriate block, so discard it and fetch desired data from memory (cache always copy)

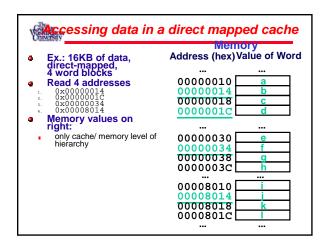

| 4 Addresses:                                                    |           |                    |

|-----------------------------------------------------------------|-----------|--------------------|

| ox00000014, 0x00                                                |           |                    |

| 0x0000034, 0x00                                                 | 008014    |                    |

| <ul> <li>4 Addresses divide<br/>Index, Byte Offset f</li> </ul> |           | enience) into Tag, |

|                                                                 |           |                    |

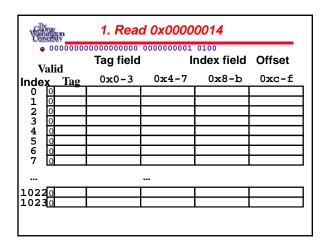

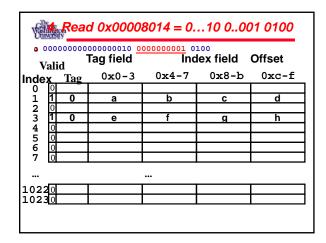

| 000000000000000000000000000000000000000                         | 000000001 | 0100               |

| 000000000000000000000000000000000000000                         | 000000001 | 1100               |

| 000000000000000000000000000000000000000                         | 000000011 | 0100               |

| 000000000000000000000000000000000000000                         | 000000001 | 0100               |

| Tag                                                             | Index     | Offset             |

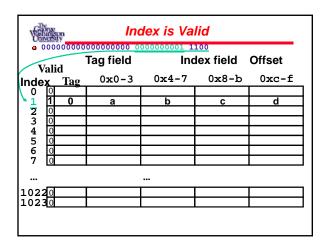

| Unixe         |                       | 00000000000 | 000000001 | 0100       |        |

|---------------|-----------------------|-------------|-----------|------------|--------|

| -             |                       |             |           | ndex field | Offset |

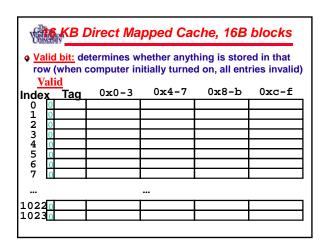

| Va<br>Idex    | h <del>d</del><br>Tag | 0x0-3       | 0x4-7     | 0x8-b      | 0xc-f  |

| 0             |                       |             |           |            |        |

| $\frac{1}{2}$ |                       |             |           |            |        |

| 3             | )                     |             |           |            |        |

| 4             |                       |             |           |            |        |

| 6 0           |                       |             |           |            |        |

| 7 0           | -                     |             |           |            |        |

|               |                       |             |           |            |        |

| 022           | D                     |             |           |            |        |

| 023           | )                     |             |           |            |        |

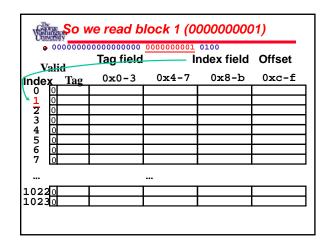

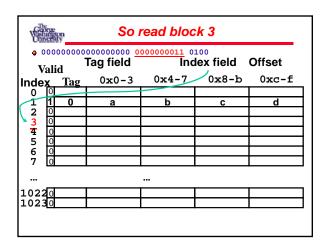

| ٠       | 000000              | 000000000000000000000000000000000000000 |       |            |        |

|---------|---------------------|-----------------------------------------|-------|------------|--------|

| v       | alid                | Tag field                               | l II  | ndex field | Offset |

|         | anu<br><u>x Tag</u> | 0x0-3                                   | 0x4-7 | 0x8-b      | 0xc-f  |

| 0       | 0                   |                                         | h     |            | a -    |

| 1234567 | 0                   | а                                       | b     | C          | a      |

| 3       | 0                   | 1                                       |       |            |        |

| 4       | 0                   |                                         |       |            |        |

| 5       | 0<br>0              |                                         |       |            |        |

| 7       | 0                   |                                         |       |            |        |

|         |                     |                                         |       |            |        |

| L022    |                     | 1                                       |       |            |        |

| 1023    |                     |                                         |       |            |        |

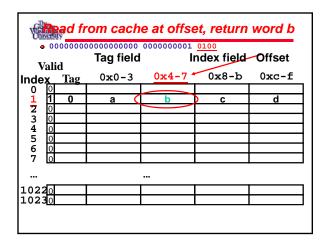

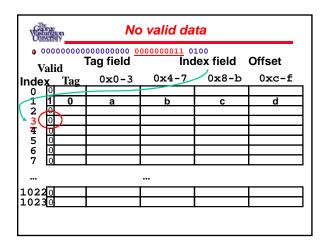

| <ul> <li>000000000</li> </ul>                   | 000000000000000000000000000000000000000 | lid, Tag l |           |        |

|-------------------------------------------------|-----------------------------------------|------------|-----------|--------|

| Valid                                           | Tag field                               | Inc        | lex field | Offset |

| Index Tag                                       | 0x0-3                                   | 0x4-7      | 0x8-b     | 0xc-f  |

| 0 0 7<br>2 0<br>3 0<br>4 0<br>5 0<br>6 0<br>7 0 | a                                       | b          | C         | d      |

| <br>10220<br>10230                              |                                         |            |           |        |

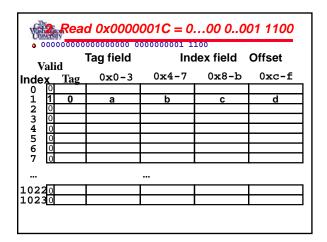

| 0 0     |       | Tag field |       | 100<br>Jex field | Offset |

|---------|-------|-----------|-------|------------------|--------|

|         | 'alid | 0x0-3     |       | 0x8-b            | 0xc-f  |

| Inde    | x Tag | 0x0-3     | 011-7 | C-0X0            | UNC-1  |

| 01      | 1 0   | а         | b     | c 🕻              | d      |

| 2       | 0     |           |       |                  | $\sim$ |

| 3       | 0     |           |       |                  |        |

| 5       | 0     |           |       |                  |        |

| 1234567 | 0     |           |       |                  |        |

| 7       | 0     |           |       |                  |        |

|         |       |           |       |                  |        |

| 1022    | 20    |           |       |                  |        |

| 1023    | 30    |           |       |                  |        |

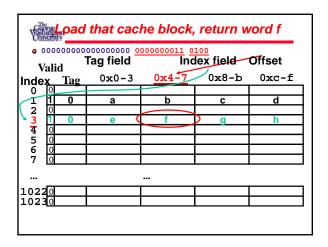

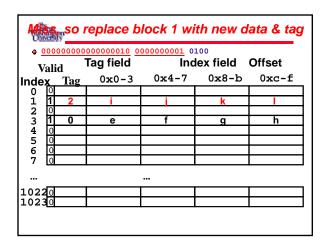

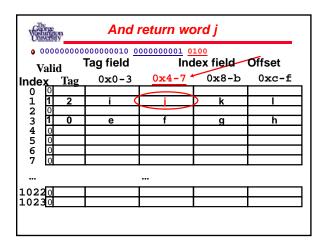

|                                      | versity                                               | d 0x0000  |       |           | 11 0100 |

|--------------------------------------|-------------------------------------------------------|-----------|-------|-----------|---------|

| v                                    | alid                                                  | Tag field | Inc   | lex field | Offset  |

|                                      | x Tag                                                 | 0x0-3     | 0x4-7 | 0x8-b     | 0xc-f   |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | 0<br>1 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | a         | b     | с<br>     |         |

| <br>1022<br>1023                     |                                                       |           |       |           |         |

| • 00<br>Val                     |   | 000000010 <u>00</u><br>Tag field |       | 100<br>lex field | Offset |

|---------------------------------|---|----------------------------------|-------|------------------|--------|

| ndex                            |   | 0x0-3                            | 0x4-7 | 0x8-b            | 0xc-f  |

| 0 0                             | 0 | а                                | b     | С                | d      |

| Ż                               | Ľ |                                  |       |                  |        |

| 3 1<br>4 0                      | 0 | е                                | T     | g                | h h    |

| 1<br>2<br>3<br>4<br>5<br>6<br>7 |   |                                  |       |                  |        |

| 7 0                             |   |                                  |       |                  |        |

|                                 |   |                                  |       |                  |        |

| 0220                            |   |                                  |       |                  |        |

| .0230                           |   |                                  |       |                  |        |

| Univ                            | ersity   |           | -     |           | h (0 != 2) |

|---------------------------------|----------|-----------|-------|-----------|------------|

|                                 |          | Tag field |       | lex field | Offset     |

| Index                           |          | 0x0-3     | 0x4-7 | 0x8-b     | 0xc-f      |

| 0                               | 0<br>1 0 | а         | b     | c         | d          |

| 1<br>2<br>3<br>4<br>5<br>6<br>7 | 0<br>1 0 | е         | f     | g         | h          |

| 4<br>5                          | 0        |           |       |           |            |

| 6<br>7                          | 0<br>0   |           |       |           |            |

|                                 |          |           |       |           |            |

| 1022<br>1023                    |          |           |       |           |            |

|                                 |          |           |       |           |            |

|                                 |          |           |       |           |            |

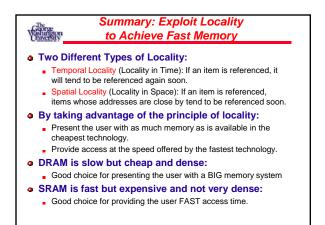

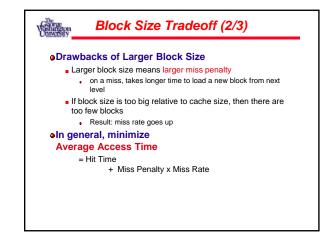

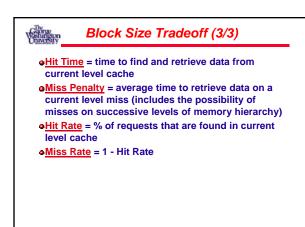

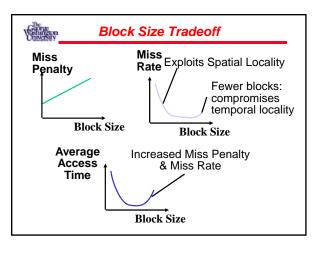

### Block Size Tradeoff (1/3)

### •Benefits of Larger Block Size

- <u>Spatial Locality</u>: if we access a given word, we're likely to access other nearby words soon

- Very applicable with Stored-Program Concept: if we execute a given instruction, it's likely that we'll execute the next few as well

- . Works nicely in sequential array accesses too

# Fully Associative Cache (1/3)

### • Memory address fields:

- Tag: same as before

- Offset: same as before

- Index: non-existant

### • What does this mean?

- no "rows": any block can go anywhere in the cache

- must compare with all tags in entire cache to see if data is there

#### Fully Associative Cache (2/3) **Grully Associative Cache (e.g., 32 B block)** compare tags in parallel Cache Tag (27 bits long) Byte Offset **Cache Data** Valid Cache Tag **B1 B 0** Ð B 31 Θ Ð : : :

# Fully Associative Cache (3/3)

### Benefit of Fully Assoc Cache

• No Conflict Misses (since data can go anywhere)

### Drawbacks of Fully Assoc Cache

Need hardware comparator for every single entry: if we have a 64KB of data in cache with 4B entries, we need 16K comparators: infeasible

### Third Type of Cache Miss

### Capacity Misses

- niss that occurs because the cache has a limited size

- miss that would not occur if we increase the size of the cache

- sketchy definition, so just get the general idea

- •This is the primary type of miss for Fully Associative caches.

# N-Way Set Associative Cache (1/4)

### •Memory address fields:

- Tag: same as before

- Offset: same as before

- Index: points us to the correct "row" (called a set in this case)

- •So what's the difference?

### each set contains multiple blocks

once we've found correct set, must compare with all tags in that set to find our data

# N-Way Set Associative Cache (2/4)

#### •Summary:

- cache is direct-mapped w/respect to sets

- each set is fully associative

## N-Way Set Associative Cache (3/4)

### •Given memory address:

- Find correct set using Index value.

- Compare Tag with all Tag values in the determined set.

- If a match occurs, hit!, otherwise a miss.

- Finally, use the offset field as usual to find the desired data within the block.

# Way Set Associative Cache (4/4)

### •What's so great about this?

even a 2-way set assoc cache avoids a lot of conflict misses hardware cost isn't that bad: only need N comparators

#### oIn fact, for a cache with M blocks,

- it's Direct-Mapped if it's 1-way set assoc

- it's Fully Assoc if it's M-way set assoc

- so these two are just special cases of the more general set associative design

#### Wishington Cache Things to Remember

- Caches are NOT mandatory: Processor performs arithmetic Processor performs arithmetic

Memory stores data

Caches simply make data transfers go *faster*

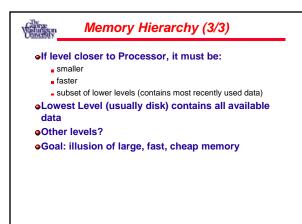

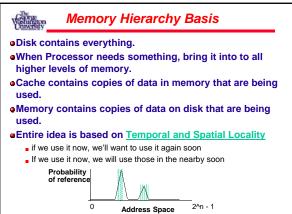

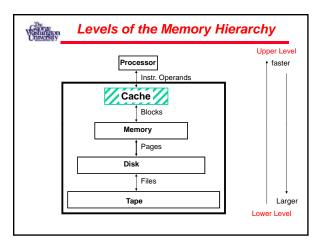

- Each level of Memory Hiererarchy is a subset of next higher level

- Caches speed up due to temporal locality: store data used recently

- Block size > 1 wd spatial locality speedup: Store words next to the ones used recently

- Cache design choices: size of cache: speed v. capacity N-way set assoc: choice of N (direct-mapped, fully-associative just special cases for N)

## Block Replacement Policy (1/2)

- Direct-Mapped Cache: index completely specifies position which position a block can go in on a miss

- N-Way Set Assoc: index specifies a set, but block can occupy any position within the set on a miss

- •Fully Associative: block can be written into any position

- •Question: if we have the choice, where should we write an incoming block?

## Block Replacement Policy (2/2)

- olf there are any locations with valid bit off (empty), then usually write the new block into the first one.

- olf all possible locations already have a valid block, we must pick a replacement policy: rule by which we determine which block gets "cached out" on a miss.

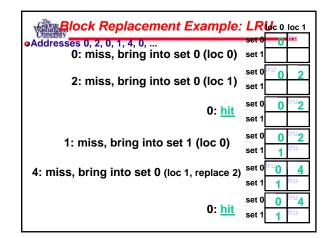

# Block Replacement Policy: LRU

### LRU (Least Recently Used)

- Idea: cache out block which has been accessed (read or write) least recently

- Pro: temporal locality  $\Rightarrow$  recent past use implies likely future use: in fact, this is a very effective policy

- Con: with 2-way set assoc, easy to keep track (one LRU bit); with 4-way or greater, requires complicated hardware and much time to keep track of this

## Block Replacement Example

•We have a 2-way set associative cache with a four word <u>total</u> capacity and one word blocks. We perform the following word accesses (ignore bytes for this problem):

0, 2, 0, 1, 4, 0, 2, 3, 5, 4 How many hits and how many misses will there be for the LRU block replacement policy?

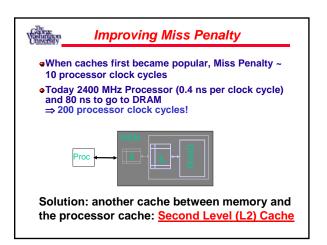

| Manag<br>by com            |              |              | Mana<br>by har                 | •             | ha           | iged b<br>ardwa<br>plicat  | re,              |

|----------------------------|--------------|--------------|--------------------------------|---------------|--------------|----------------------------|------------------|

| 07                         | Reg          | L1 Inst      | L1 Data                        | L2            | DRAM         | Disk                       |                  |

| Size                       | 1K           | 64K          | 32K                            | 512K          | 256M         | 80G                        | _                |

| Latency<br>Cycles,<br>Time | 1,<br>0.6 ns | 3,<br>1.9 ns | 3,<br>1.9 ns                   | 11,<br>6.9 ns | 88,<br>55 ns | 10 <sup>7</sup> ,<br>12 ms | iMac (<br>1.6 GH |

| Goal:                      | Illusio      | n of la      | rge, fas                       | st, chea      | ap mer       | nory                       |                  |

| scale                      | es to th     | ne disk      | ess a m<br>size, a<br>t as reg | t a spe       | ed that      |                            |                  |